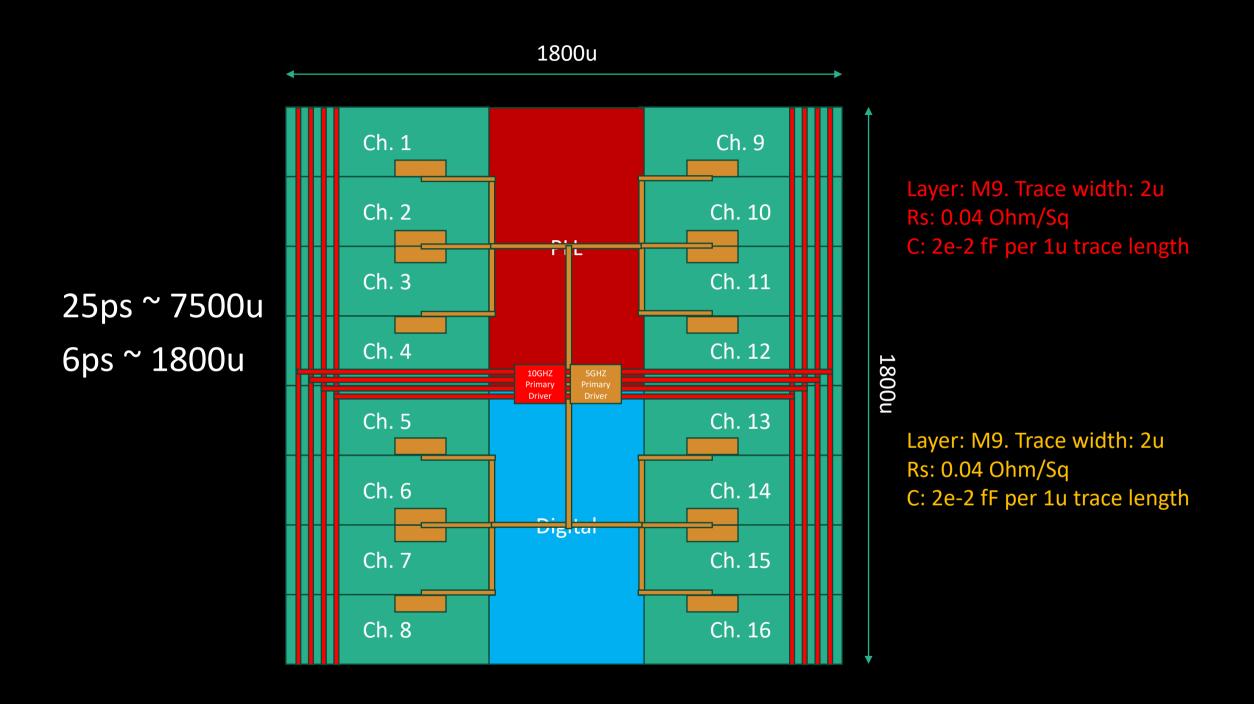

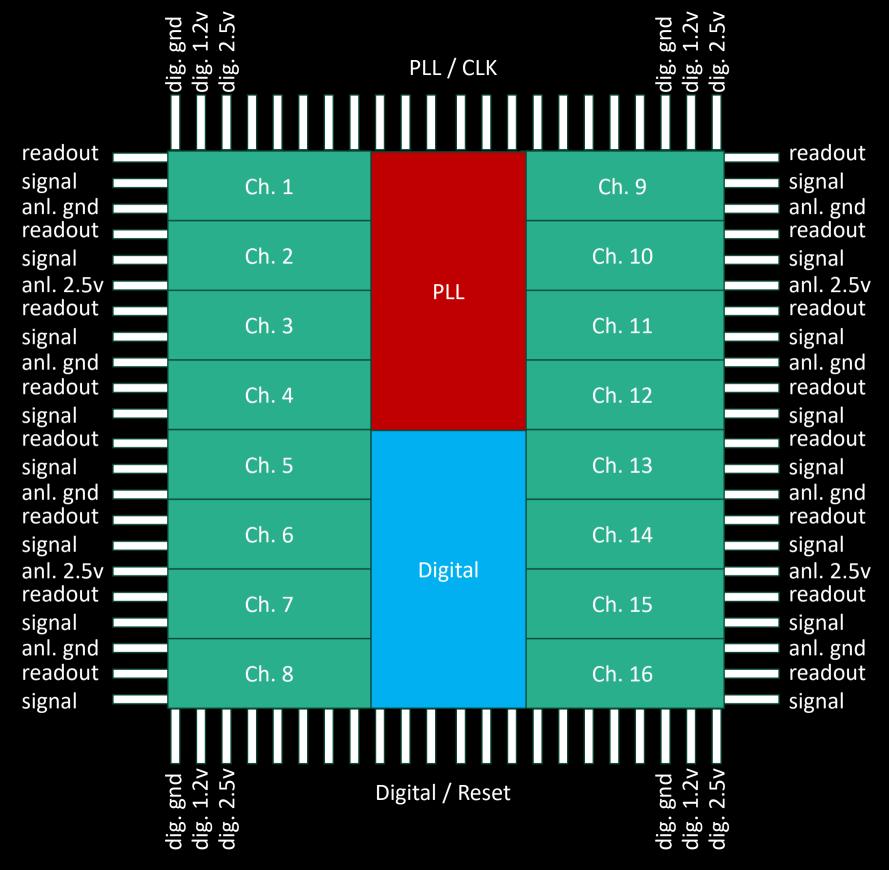

# PSEC5 Layout

Dec 2023

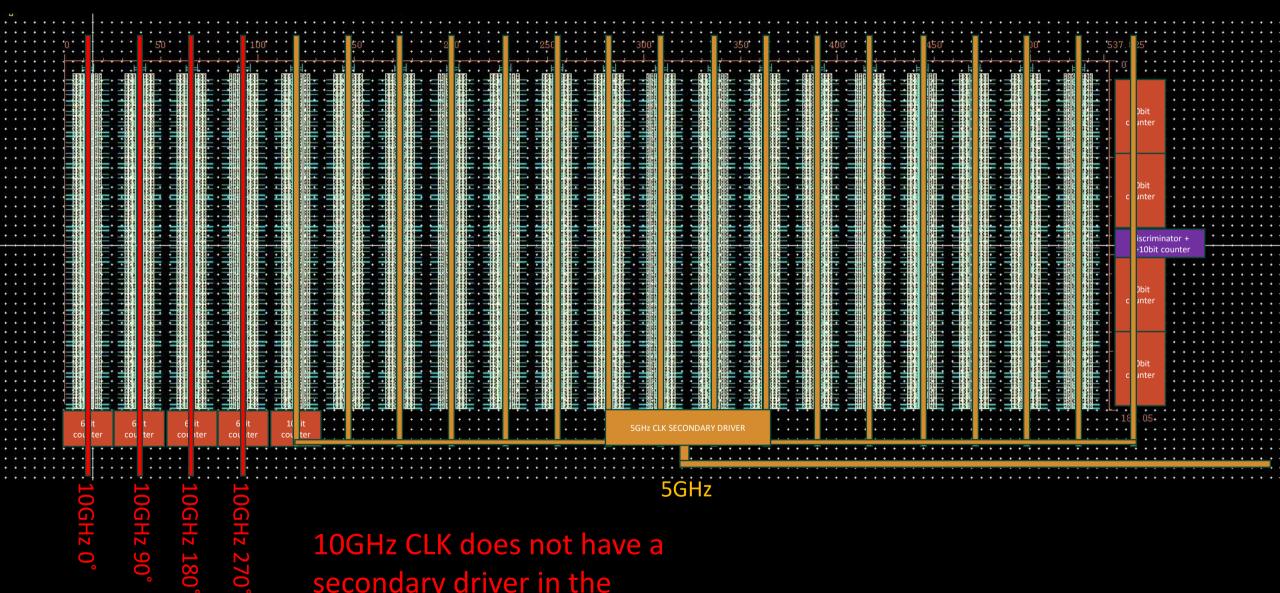

# Single Channel Overview

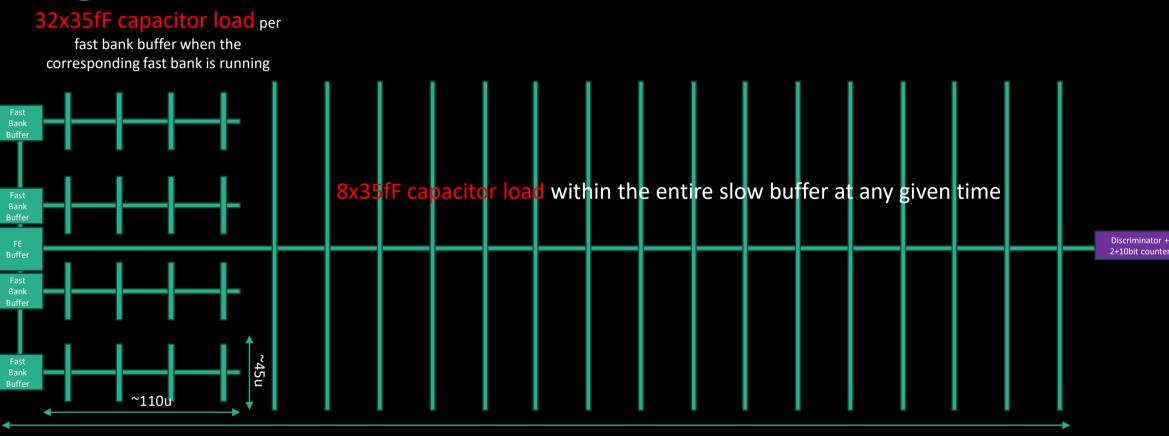

|                          |                 | ••••• |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          |                                       |

|--------------------------|-----------------|-------|---------------------------|------------------|----|-----|---------------------------------------|-----|---------------|---------------------------------------|---------------------------------------|----------------------------------------------------------|---------------------------------------|

| : <u>;</u>               |                 |       | 100                       |                  | 50 | 200 | 250                                   | 300 | 350           | 400                                   | 450                                   | :::::::::::::::::::::::::::::::::::::::                  | 37.825                                |

| Readout<br>Buffer        |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          |                                       |

| • Fast<br>Bank<br>Buffer |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          | 10bit<br>counter                      |

| Fast<br>Bank             |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          | 10bit<br>counter                      |

| Buffer<br>FE<br>Buffer   |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          | Discriminator +<br>2+10bit counter    |

| Fast<br>Bank<br>Buffer   |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          | 10bit<br>counter                      |

|                          |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          |                                       |

| Fast<br>Bank<br>Buffer   |                 |       |                           |                  |    |     |                                       |     |               |                                       |                                       |                                                          | 10bit<br>counter                      |

|                          | 6bit<br>counter |       | bit 6bit<br>inter counter | 10bit<br>counter |    |     |                                       |     | Hz CLK DRIVER |                                       |                                       | ₩ <u>₩</u> ;_ <b>₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩₩</b> | 180.05                                |

|                          |                 |       |                           |                  |    |     | · · · · · · · · · · · · · · · · · · · |     |               | • • • • • • • • • • • • • • • • • • • | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·                    | · · · · · · · · · · · · · · · · · · · |

# Signal Transmission

~550u

Layer: M6. Trace width: 2u Rs: 0.14 Ohm/Sq C: 2e-2 fF per 1u trace length

# Trigger Scheme

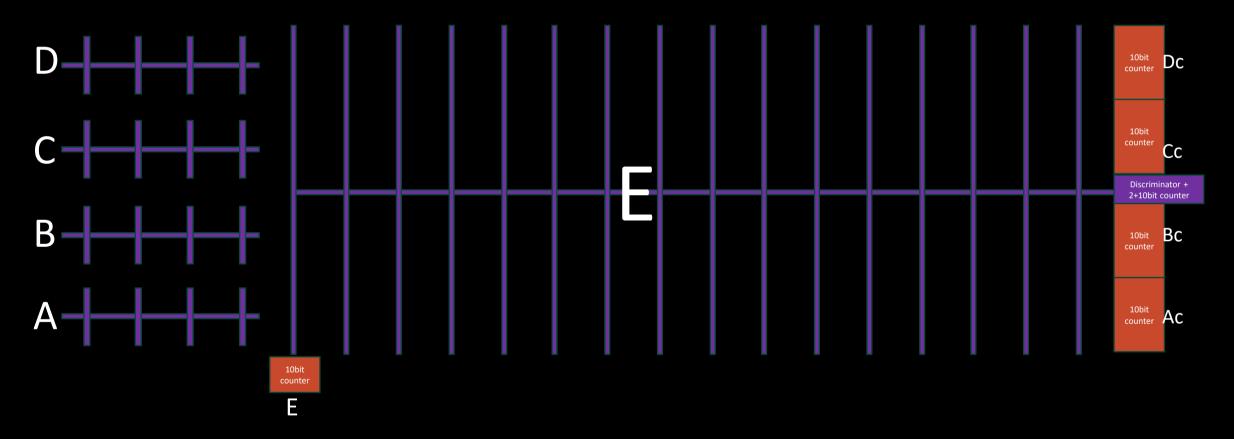

0: sampling and counting. 1: holding and not counting.

#### States and Trigger Scheme

| States          | Α     | Ac                             | В | Вс | C                              | Сс | D | Dc | E |  |  |

|-----------------|-------|--------------------------------|---|----|--------------------------------|----|---|----|---|--|--|

| stopped         | 1     | 1                              | 1 | 1  | 1                              | 1  | 1 | 1  | 1 |  |  |

| samplingA       | 0     | 0                              | 1 | 0  | 1                              | 0  | 1 | 0  | 0 |  |  |

| samplingB       | 1     | 1                              | 0 | 0  | 1                              | 0  | 1 | 0  | 0 |  |  |

| samplingC       | 1     | 1                              | 1 | 1  | 0                              | 0  | 1 | 0  | 0 |  |  |

| samplingD       | 1     | 1                              | 1 | 1  | 1                              | 1  | 0 | 0  | 0 |  |  |

| samplingE       | 1     | 1                              | 1 | 1  | 1                              | 1  | 1 | 1  | 0 |  |  |

| samplingA+B     | 0     | 0                              | 0 | 0  | 1                              | 0  | 1 | 0  | 0 |  |  |

| samplingC+D     | 1     | 1                              | 1 | 1  | 0                              | 0  | 0 | 0  | 0 |  |  |

| samplingA+B+C+D | 0     | 0                              | 0 | 0  | 0                              | 0  | 0 | 0  | 0 |  |  |

| Tr              |       | Conditions                     |   |    |                                |    |   |    |   |  |  |

| stoppe          |       | Start command from FPGA        |   |    |                                |    |   |    |   |  |  |

| sampling        | gA→sa | mpling                         | В |    | Discri. Fired for the 1st time |    |   |    |   |  |  |

| sampling        | gB→sa | mpling                         | C |    | Discri. Fired for the 2nd time |    |   |    |   |  |  |

| sampling        | gC→sa | mpling                         | D |    | Discri. Fired for the 3rd time |    |   |    |   |  |  |

| samplin         |       | Discri. Fired for the 4th time |   |    |                                |    |   |    |   |  |  |

| samplingE       |       | Stop command from FPGA         |   |    |                                |    |   |    |   |  |  |

After roughly 800 5GHz clock cycles or 180ns since the discriminator fired for the 1<sup>st</sup> time, notify the FPGA so that it can issue the stop command

# **Readout Scheme**

There is a voltage follower at each column, 20 in total.

| Readout<br>Buffer | <b>L<u>A</u>NAN</b> |  | ΠΔΠΔ | <u>n An A</u> r |  |

|-------------------|---------------------|--|------|-----------------|--|

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

|                   |                     |  |      |                 |  |

Each thick blue line represents 64 flip-flops running at 50MHz. Only one flip-flop is high at any given time.

### **Clock distribution**

10GHz CLK does not have a secondary driver in the current design!