# Design of a 16 Channel 40 GS/sec 10 mW/Channel Waveform Sampling ASIC in 65 nm CMOS

```

Jinseo Park<sup>2</sup>,

```

D. Braga<sup>1</sup>, F. Fahim<sup>1</sup>, N. J. Pastika<sup>1</sup>, P. M. Rubinov<sup>1</sup>, T. N. Zimmerman<sup>1</sup>,

H. J. Frisch<sup>2</sup>, M. Heintz<sup>2</sup>, E. Oberla<sup>2</sup>, C. Poe<sup>2</sup>, Y. R. Yeung<sup>2</sup>,

C. Ertley<sup>3</sup>, N. Sullivan<sup>4</sup>,

E. Angelico<sup>5</sup>,

Hector Rico-Aniles<sup>6</sup>

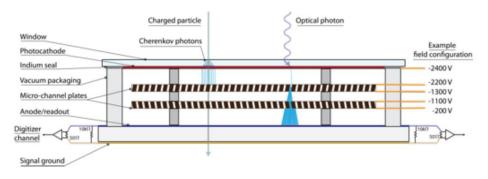

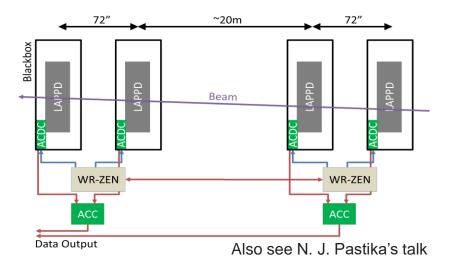

#### Motivation: Detectors with ps resolution

$\mathsf{LAPPD}^{\mathsf{TM}},\,\mathsf{psec.uchicago.edu}$

Perazzini S, Ferrari F, Vagnoni VM, on behalf of the LHCb ECAL Upgrade-2 R&D Group. Development of an MCP-Based Timing Layer for the LHCb ECAL Upgrade-2

Timing resolution ~5ps

#### ...WE ALSO NEED SUB-PS RESOLUTION FE ELECTRONICS!

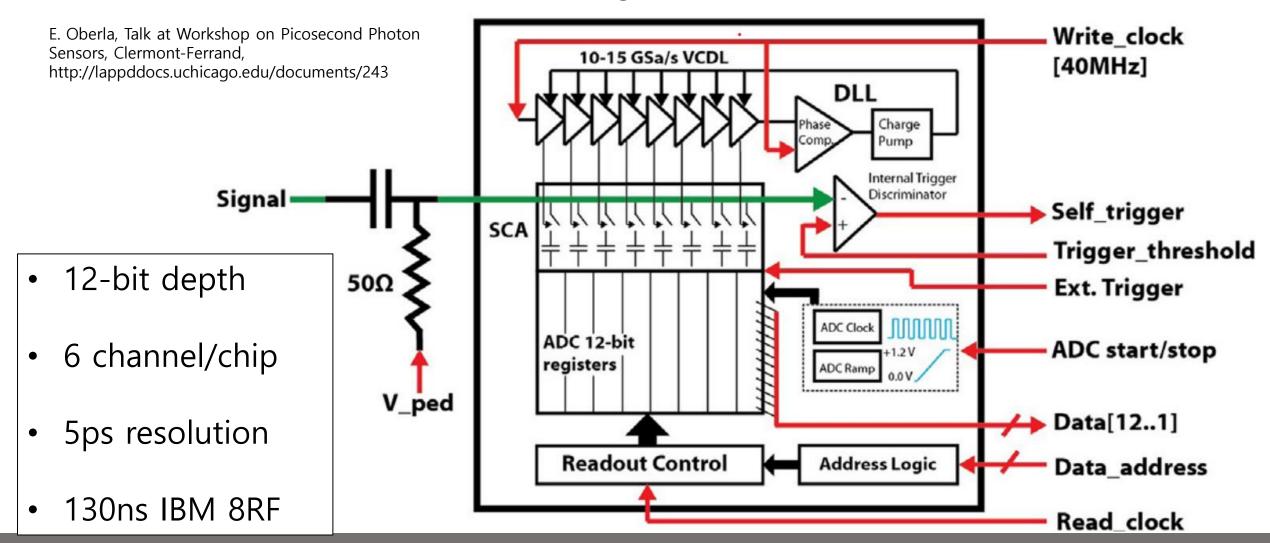

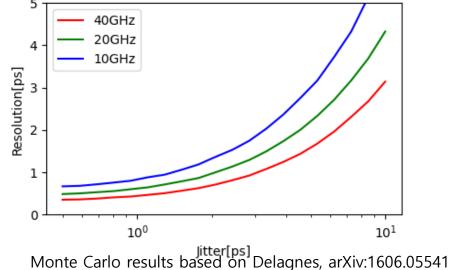

#### PSEC4 ASIC(2014)

E. Oberla, H. Frisch, K. Nishimura, G. Varner, arxiv.org/abs/1309.4397

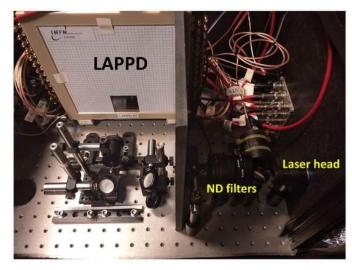

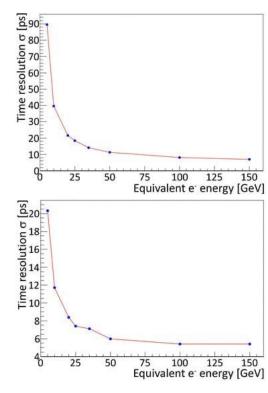

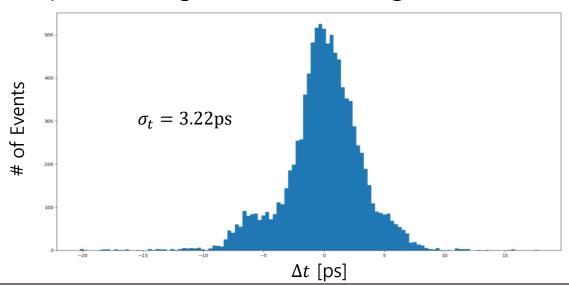

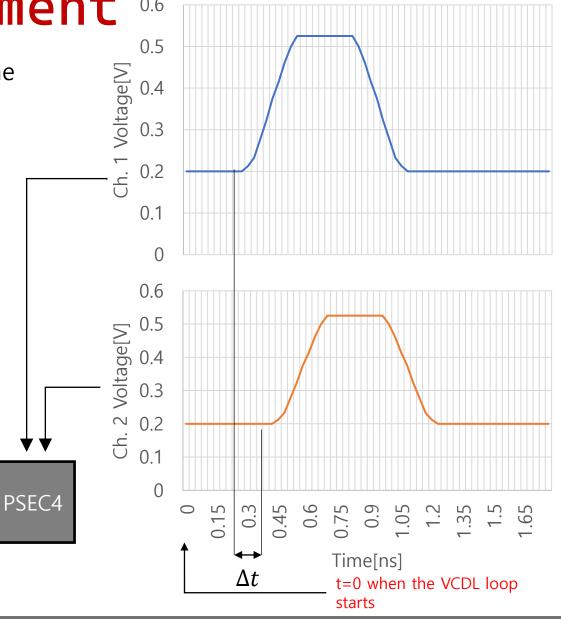

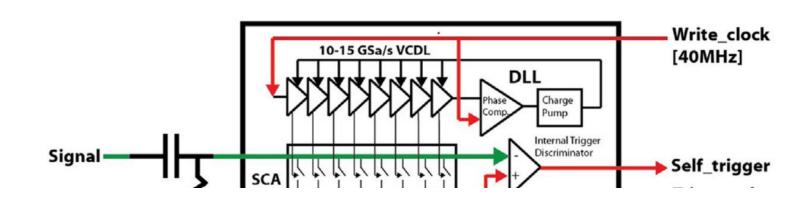

Performance Measurement

Same signal fed into two different channels of the same readout board.

- 1.  $\Delta t$  measured for many events.

- 2. Distribution of  $\Delta t$  acquired.

Depends on the source

- Sin

- Pulse/square

Depends on algorithm determining  $\Delta t$ .

## Primary goal

Achieve <1ps resolution in measuring the arrival time of LAPPD pulses.

But we also aim for a versatile chip, so that it is applicable to other fast-timing applications

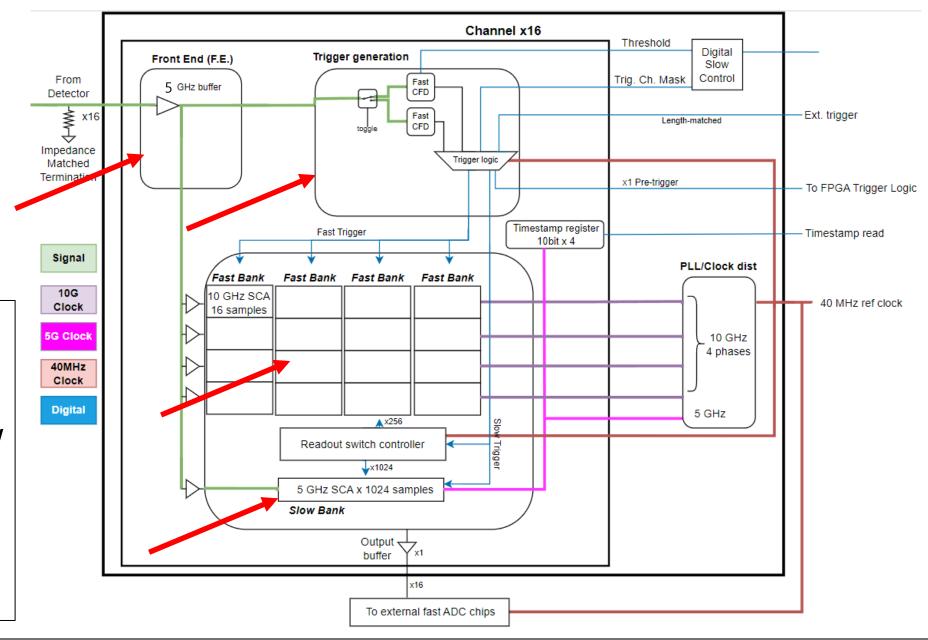

- 65nm TSMC

- 10-bit depth

- 40GSa/s

- 5GHz Analog BW

- 16 channel/chip

- <10mW/ch

- UChicago & Fermilab

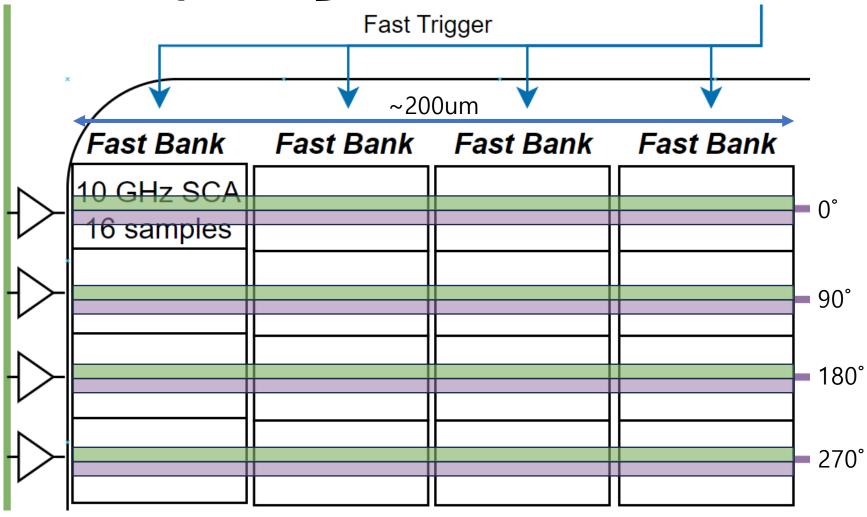

#### Point 1. Fast & Slow Banks

- Fast Bank: 4 of them

- 64 samples

- 1.6ns of sampling window

- High power consumption

- Run sequentially

- Slow Bank (Timestamp)

- 1024 samples

- 204.8ns of sampling window

- Low power consumption

- Fast banks are triggered within the sampling window

## Fast sampling - interleaved

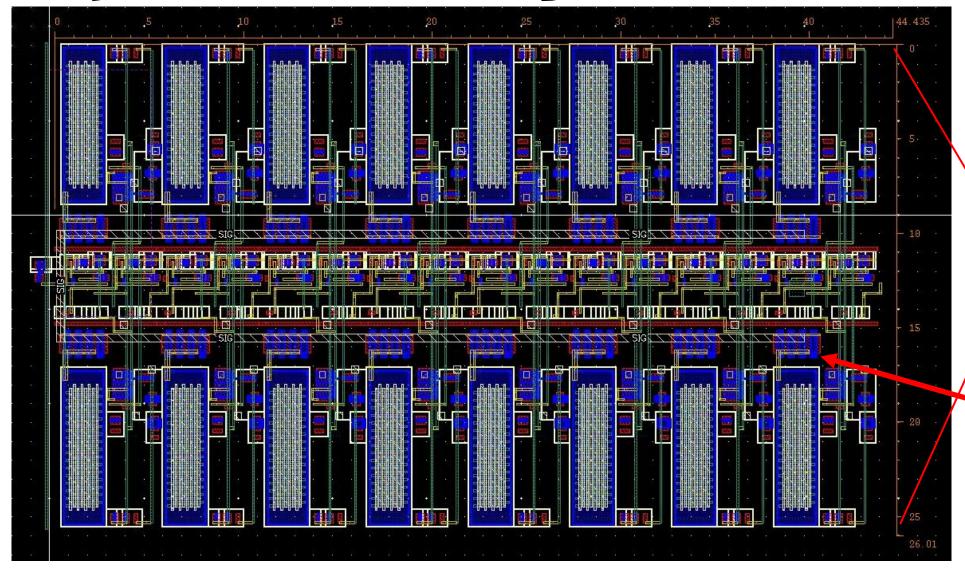

## Layout of a single column (16 cells)

Size:  $45\mu m \times 25\mu m$

Capacitor: 35fF

Power: 2mW

Sampling Switch 2.5V NMOS

Size:  $4\mu m \times 280nm$

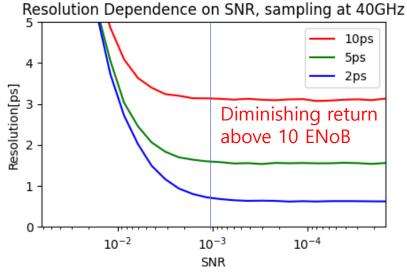

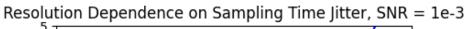

## Point 2. Sampling Jitter

At <1ps timing resolution region, sampling jitter is a dominant component of the overall uncertainty.

PSEC4 employs Delay Loop Lines (DLL) to control sampling switches.

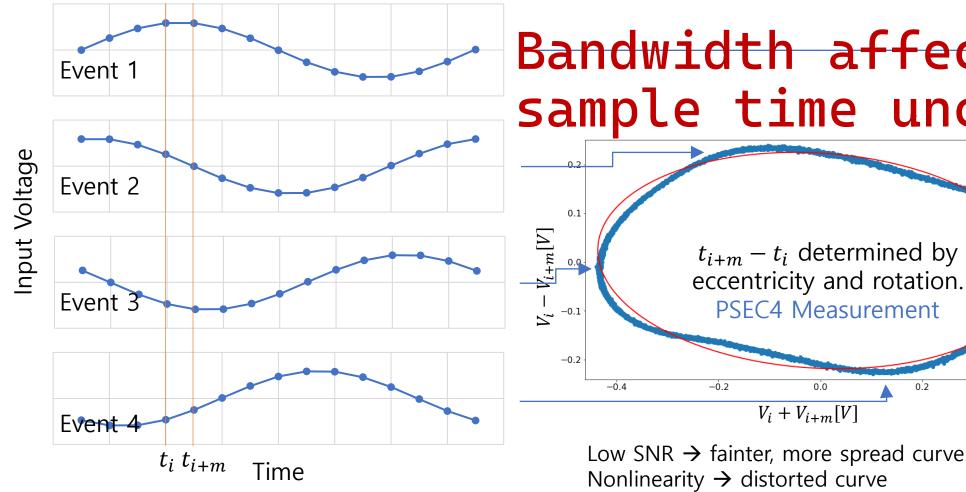

- 1. Measure many events of a sine wave.

- 2. Sum vs. Difference of two adjacent samples, over all events, form an ellipse.

- 3. Time offset can be determined from the coefficients.

Bandwidth affects sample time uncertainty!

Low SNR  $\rightarrow$  fainter, more spread curve.

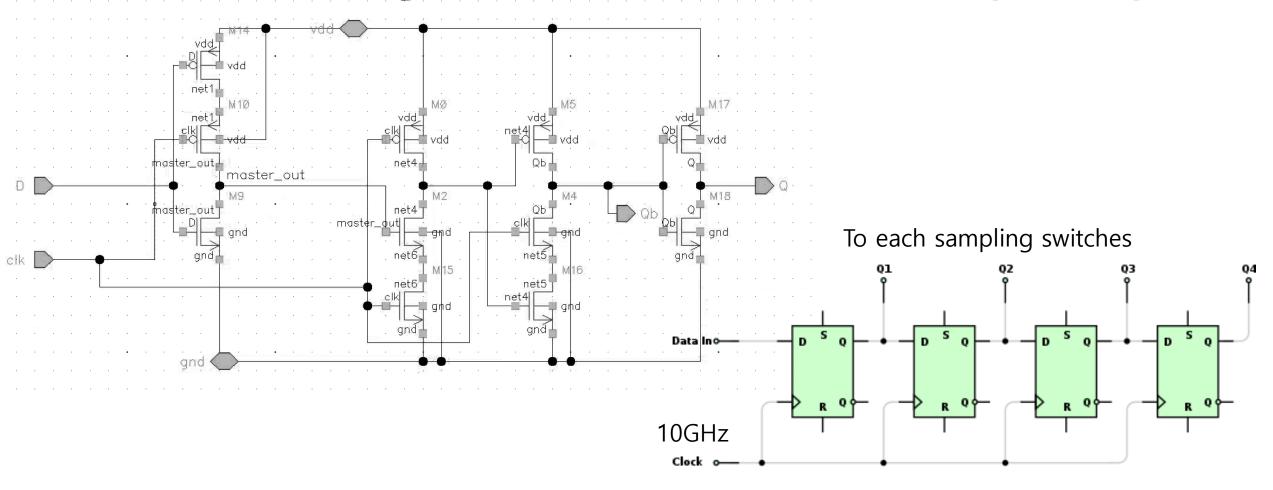

#### 10GHz True Single Phase Clock D Flip Flop

• Still, we expect to use similar calibration technique as PSEC4

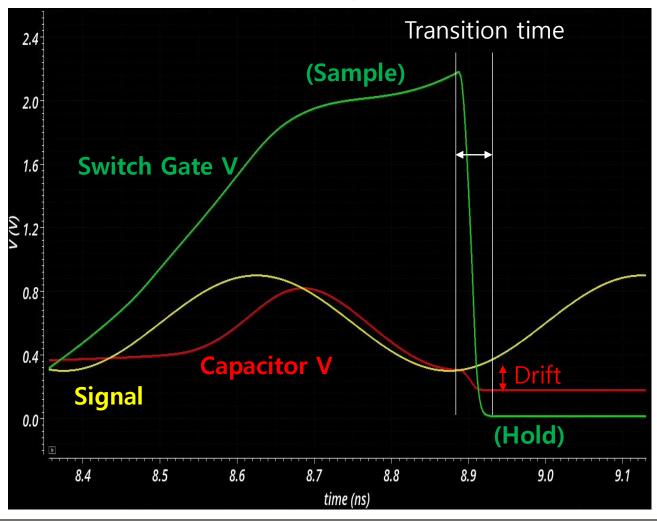

## Switching Drift

- The value of a capacitor drifts while it switches off from the signal line.

- Drift consists of switch gate charge injection, which is a fixed value and is calibratable, and resistive drift, which is dependent on signal V.

- It is essential to keep the

[Sample → Hold] transition time low.

→NMOS instead of CMOS for the sampling switch!

#### Summary

- MCP-based detectors can reach excellent timing resolution, and for a working ToF system with it, we want <1ps timing resolution of the front-end electronics.</li>

- We think a waveform sampling ASIC is the most reliable, reusable, and cost-efficient solution.

- Lower power consumption and dead time

- Avails various methods of external calibration

- **High channel count** per chip

- The **fast-slow architecture** of the chip makes it relatively versatile

- Long time window per event

- While also achieving high timing resolution on regions of interest

- Using **D Flip Flops** instead of Delay Line improves sampling time jitter

- Discriminator/Trigger logic with low propagation delay is the key

- 65nm is an adequate technology for this

- Faster sampling speed, due to dynamic flip flops, compared to coarser technologies

- High voltage transistors available compared to smaller technologies, can achieve a high V dynamic range