# Would Psec TOF Be Useful To LHCb?

Henry J. Frisch Enrico Fermi Institute University of Chicago

#### OUTLINE

What would you do with it if you had it?

How does one get much better time resolution?

Some technical details

Plan for the future- 3yr development

Apologies for sloppy talk- I finished the big DOE proposal today

#### What would TOF<10psec do for you?

- (disclaimer- I know next to nothing about LHCb, b-physics, or the Collab. goals..- I'm making this up....needs work- would be delighted to see someone pick this up.)

- If you can stand a little active material in front of your em calorimeter, convert photons- 10 psec is 3mm IN THE DIRECTION of the photon flight path- can vertex photons. Do pizeros, etas, K<sub>L</sub> and K<sub>S</sub>,...

- 2. This allows all neutral signature mass reconstruction- new channels.

e.g. the CP asymmetry in BS->π K<sup>0</sup> (J.Rosner suggestion)

- 3. Eta's in general are nice: e.g. **BS->J/psi eta** (again, J.R.)

- 4. With two planes and time maybe get to 1 psec,=300 microns along flight path- can one vertex from timing?

- 5. Searches for **rare heavy long-lived things** (other than b's)- need redundancy.

- 6. May help with pileup- sorting out vertices. 4/16/2009 LHCb Upgrade Meeting

#### **Performance Goals**

| Quantity                                                              | Present        | Baseline | HJF           |

|-----------------------------------------------------------------------|----------------|----------|---------------|

| Time resolution-charged<br>particles (psec)                           | 12<br>(6)(2.3* | 10       | <1            |

| Time resolution-photons (psec)                                        |                | 10       | 1-3           |

| Space resolution- charged (mm)                                        | 0.1*           | 1        | 0.1           |

| Space resolution- neutrals (mm)                                       |                | 5        | 1-3           |

| Thickness (inches)/plane                                              | 1*             | 2        | 2             |

| Cost (\$/30 sq-meters/plane)                                          | 60M\$          | 3.0M\$   | <b>1.2M\$</b> |

| Schedule for development (from $t_0$ - i.e. funding of MCP project)   |                | 3 yrs    | 5 yrs         |

|                                                                       |                |          |               |

|                                                                       |                |          |               |

| * With a 2" square Burle MCP in<br>beam- 6 psec on bench,2.3 expected |                |          |               |

| 4/16/2009 LHCb Upgrade Me                                             | eting          |          | 50            |

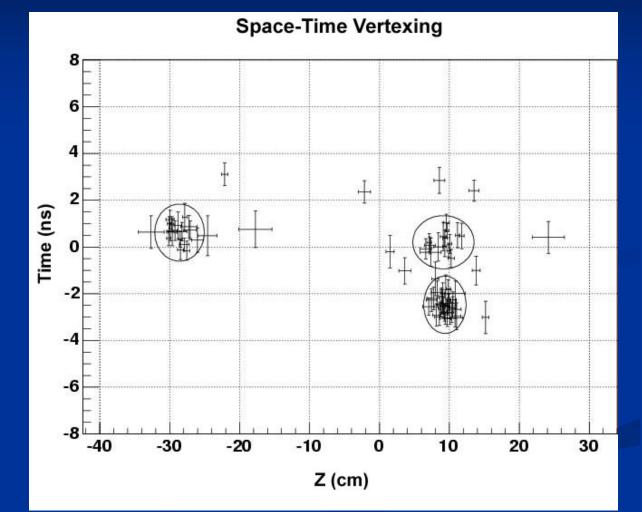

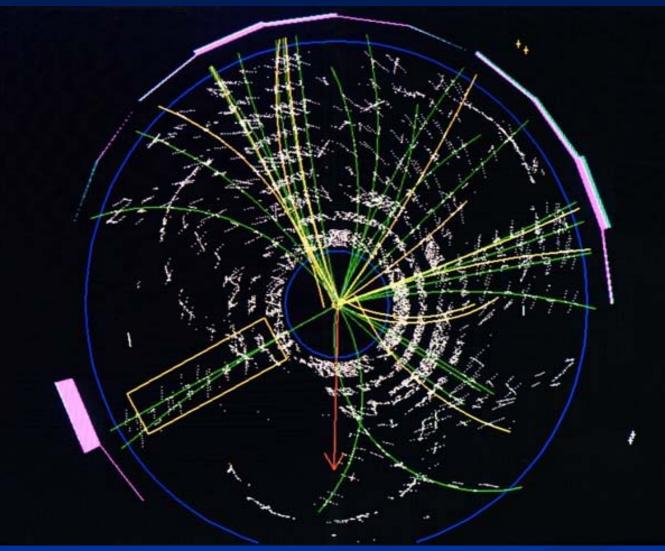

# Example of vertexing from CDF

EM timing (Dave Toback, HJF, et al) Vertices overlap in time, and in space, but usually not both Resolution is good wrt 7 cm

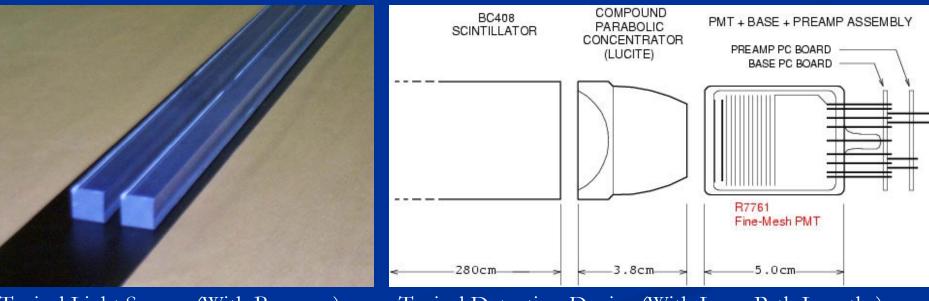

Why has 100 psec been the # for 60 yrs? Typical path lengths for light and electrons are set by physical dimensions of the light collection and amplifying device.

These are now on the order of an inch. One inch is 100 psec That's what we measure- no surprise! (pictures from T. Credo)

LHCb Upgrade Meeting

Typical Light Source (With Bounces) 4/16/2009 Typical Detection Device (With Long Path Lengths)

# Solutions: Generating the signal Use Cherenkov light - fast

Incoming rel. particle

Custom Anode with Equal-Time Transmission Lines + Capacitative. Return

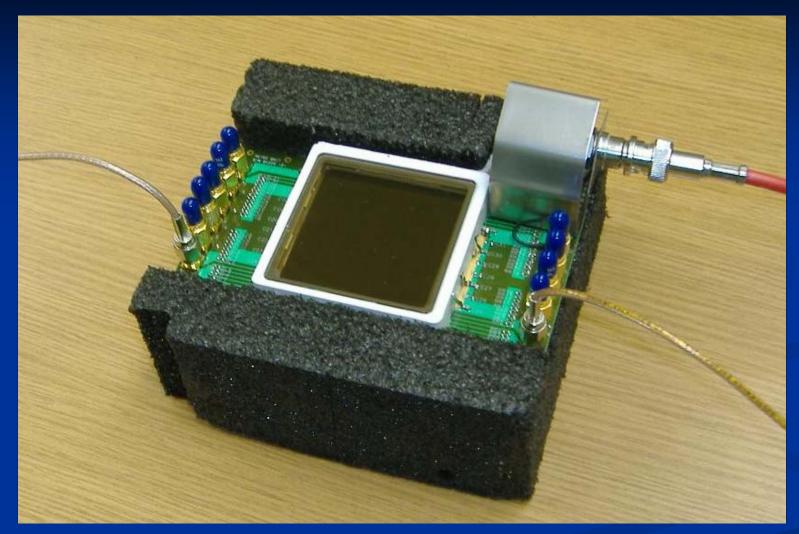

A 2" x 2" MCPactual thickness ~3/4"

e.g. Burle (Photonis) 85022with mods per our work

LHCb Upgrade Meeting

Collect charge here-differential Input to 200 GHz TDC chip<sup>53</sup>

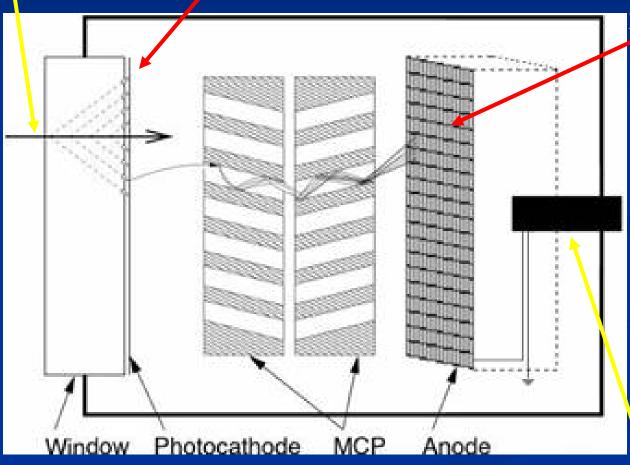

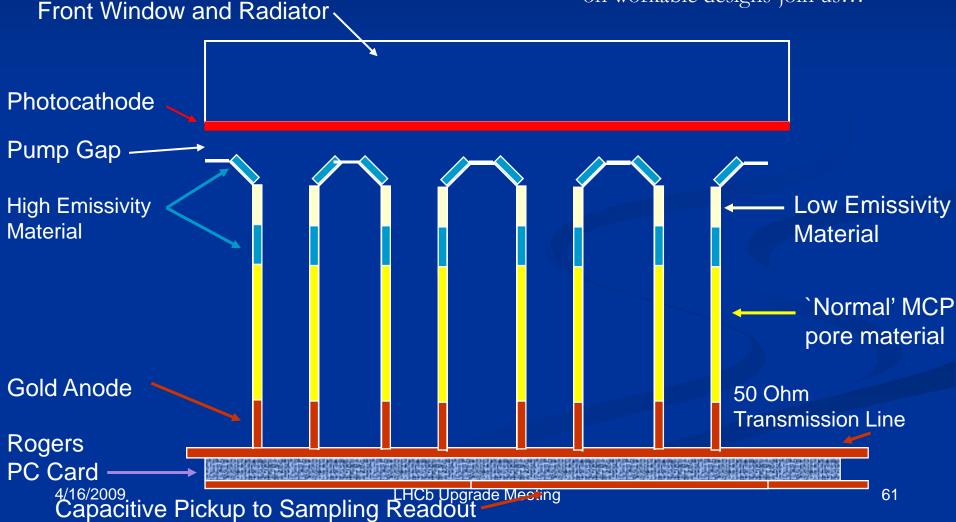

#### **Micro-channel Plates**

Currently the glass substrate has a dual function To provide the geometry and electric field like the dynode chain in a PMT, and

To use an intrinsic lead-oxide layer for secondary electron emission (SEE)

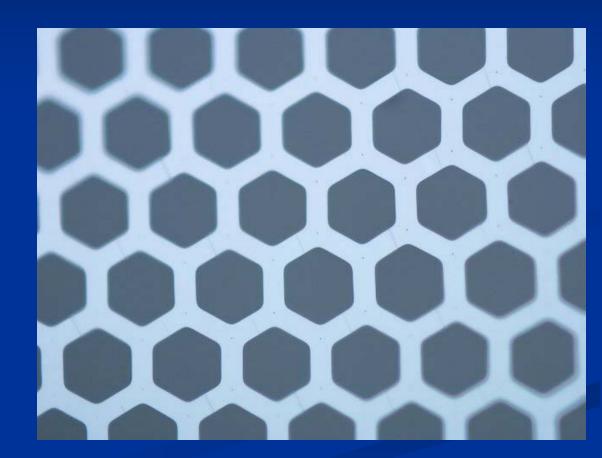

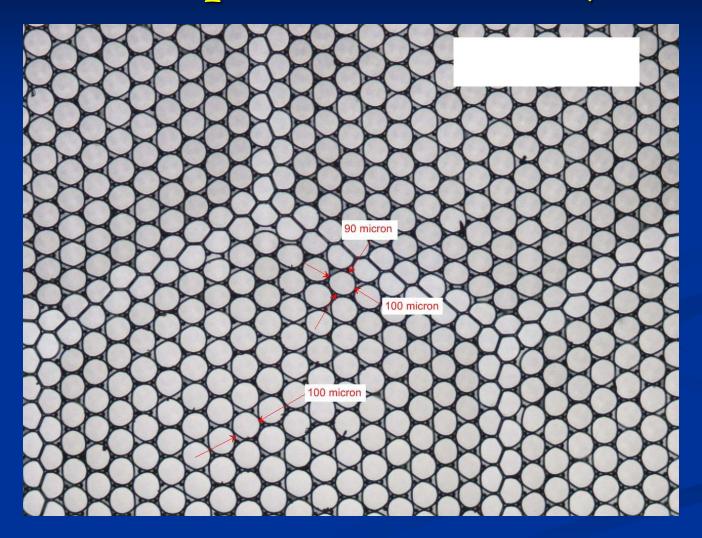

Micro-photograph of Burle 25 micron tube- Greg Sellberg (Fermilab)-~2M\$/m<sup>2</sup>- not including readout

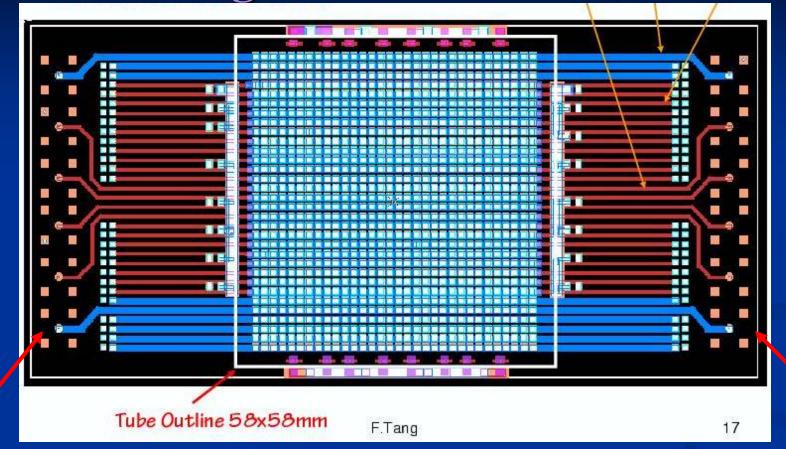

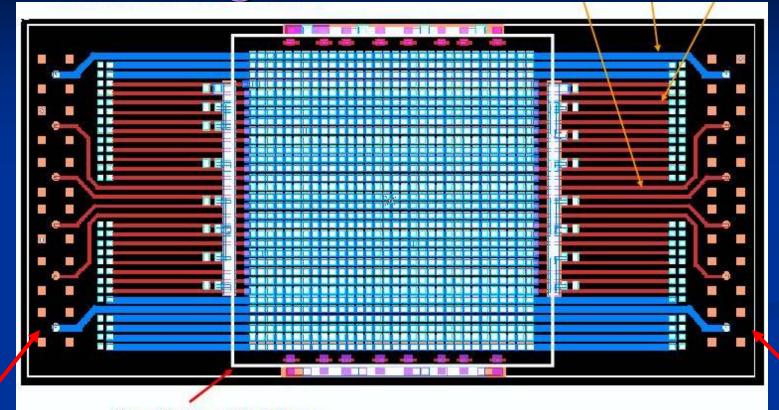

#### Get position AND time Anode Design and Simulation(Fukun Tang)

Transmission Line- readout both ends=> pos and time

Cover large areas with much reduced channel account.

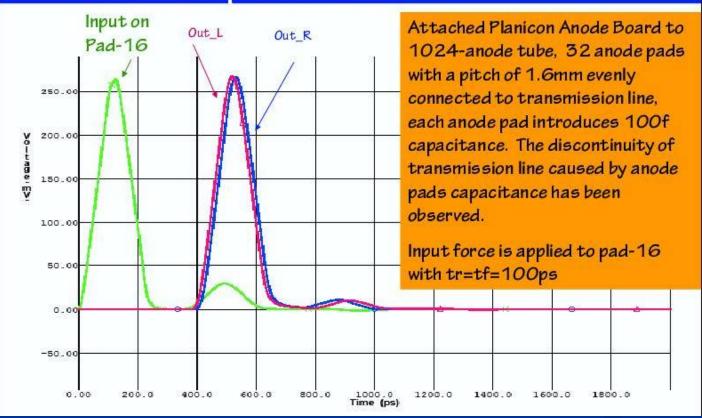

#### Comparison of measurements (Ed May and Jean-Francois Genat and simulation (Fukun Tang)

#### T32 Responses with Anode-Stubs

Transmission Line- simulation shows 3.5GHz bandwidth- 100 psec rise (well-matched to MCP)

The time difference yields a velocity of 64ps/cm against 68ps predicted

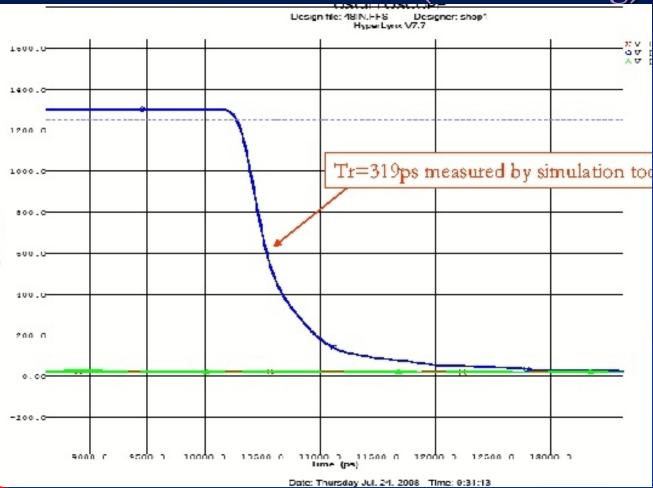

#### Scaling Performance to Large Area Anode Simulation(Fukun Tang)

48-inch Transmission Line- simulation shows 1.1 GHz bandwidth- still better than present electronics.

4/16/2009

LHCb Upgrade Meeting

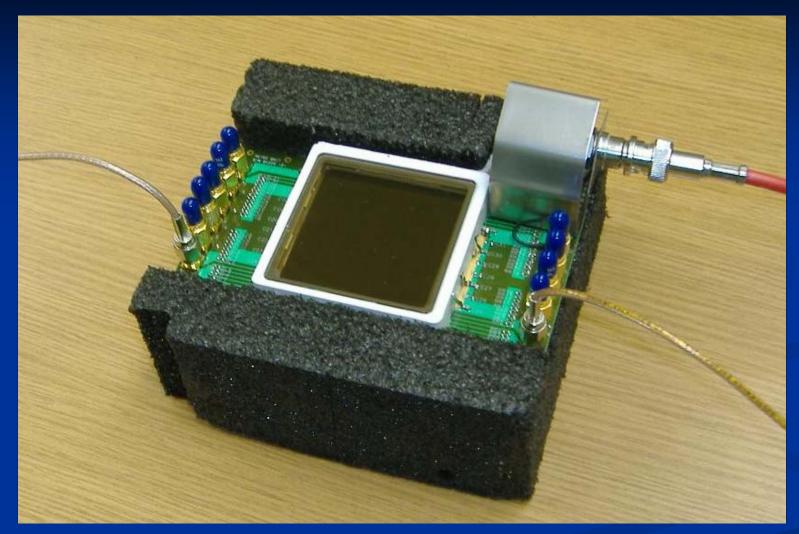

#### Photonis Planicon on Transmission Line Board

Couple 1024 pads to strip-lines with silver-loaded epoxy (Greg Sellberg, Fermilab).

4/16/2009

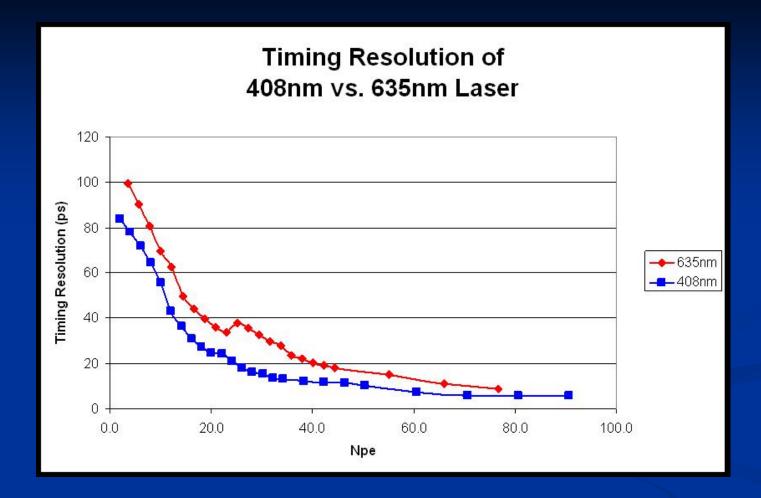

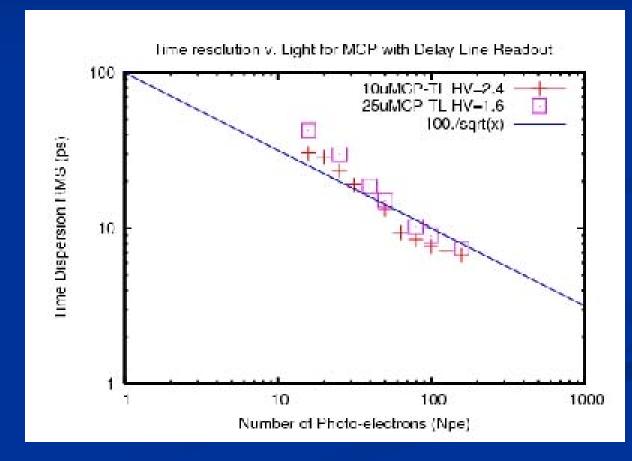

Camden Ertley results using ANL laser-test stand and commercial Burle 25-micron tube- lots of photons (note- pore size may matter less than current path!- we can do better with ALD custom designs (transmission lines)) Understanding the contributing factors to 6 psec resolutions with present Burle/Photonis/Ortec setups- Jerry Vavra's Numbers

- 1. TTS: 3.8 psec (from a TTS of 27 psec)

- 2. Cos(theta)\_cherenk 3.3 psec

- 3. Pad size 0.75 psec

- 4. Electronics 3.4 psec

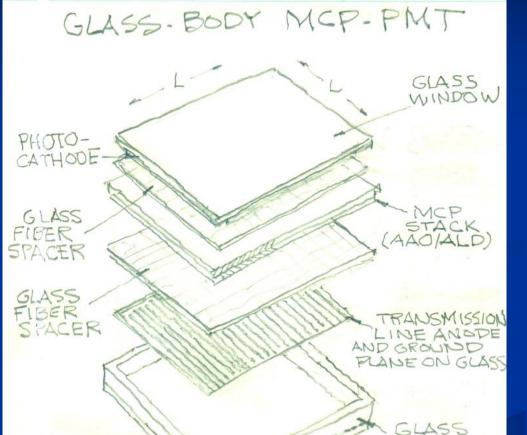

#### Large-area Micro-Channel Plate Panel "Cartoon"

N.B.- this is a `cartoon'- working on workable designs-join us...

# Incom glass capillary substrate

New technologyuse Atomic Layer Deposition to *`functionalize* an inert substratecheaper, more robust, and can even stripe to make dynode structures (?)

#### Another pore substrate (Incom)

## Front-end Electronics Critical path item- probably the reason psec detectors haven't been developed

- We had started with very fast BiCMOS designs- IBM 8HP-Tang designed two (really pretty) chips

- Realized that they are too power-hungry and too 'boutiqu for large-scale applications

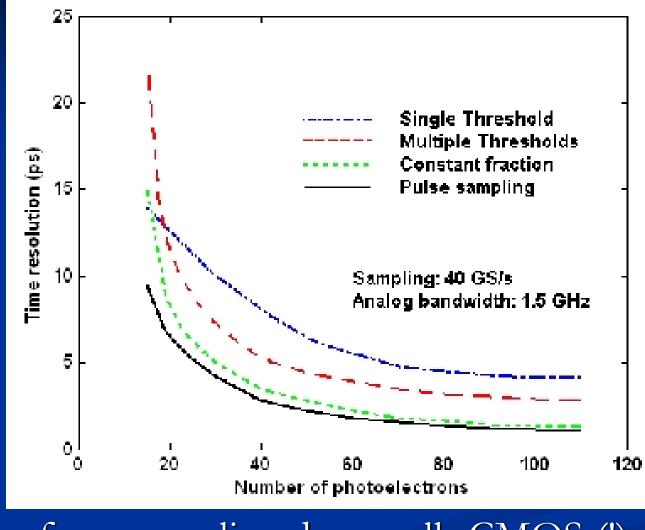

- Have been taught by Gary Varner, Stefan Ritt, Eric DeLanges, and Dominique Breton that there's a more cler and elegant way- straight CMOS – sampling onto an array of capacitors

- Have formed a collaboration to do this- have all the expert groups involved (formal with Hawaii and France)- see talks by Tang and Jean-Francois at Lyon

#### **II STATE OF THE ART**

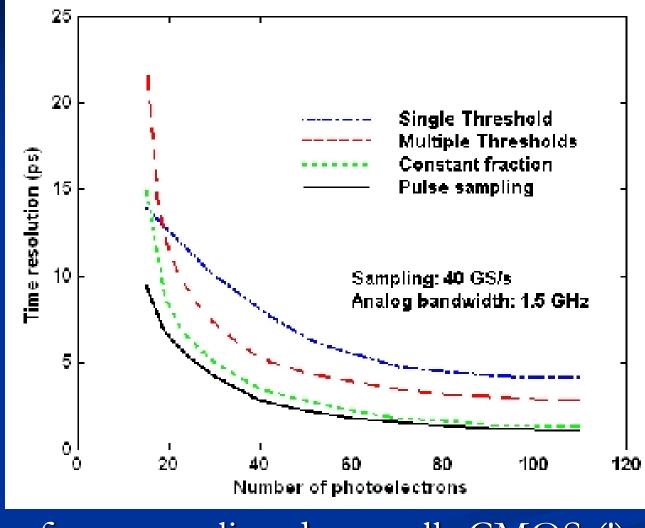

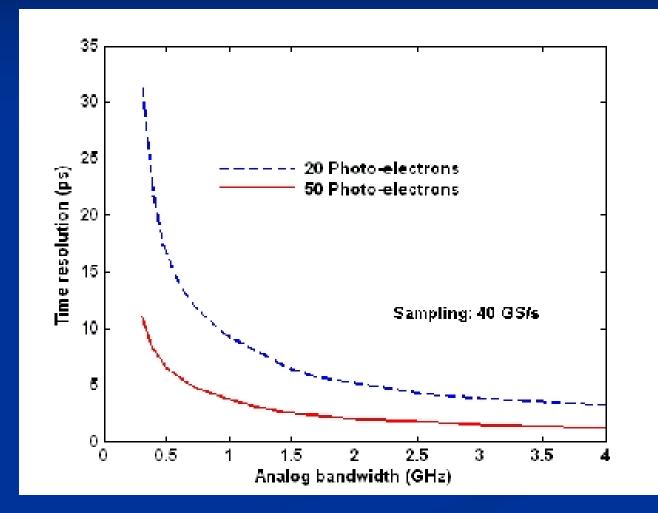

Several circuits have already been designed in the HEP community for fast pulse sampling, mainly to record photo-multipliers pulse shapes. As detailed in section I, fast timing requires higher sampling rates, but smaller dynamics ranges.

+

|                       |                   | -                          |                      |             |                     |                     |                    |

|-----------------------|-------------------|----------------------------|----------------------|-------------|---------------------|---------------------|--------------------|

|                       | Hawall            |                            | <b>Outsay/Saclay</b> |             | PSI                 |                     | PSEC               |

|                       | Lab 3             | Planned Blab2              | Sam                  | Planne<br>d | DR \$3              | Planned DRS4        | This<br>proposal   |

| Sampling frequency    | 20 MHz-3.7<br>GHz | 1-10 G Hz                  | 0.7-2.5 GHz          | 10 GHz      | 10 MHz-5 GHz        | 5GHz                | 40 GHz             |

| Analog bandwidth      | 900 MHz           | 850 MHz                    | 300 MHz              | 650<br>MHz  | 450 MHz             | > DRS3              | >1GHz              |

| Number of<br>Channels | 9                 | 16                         | 2                    |             | 12/6/2/1            | 8/4/2/1             | 16                 |

| Triggered mode        | Common Stop       | Channel trigger on<br>sums | Common Stop          |             | Common Stop         | Common Stop         | Channel<br>trigger |

| Resolution            |                   | 10 bit                     | 11.6 bit             |             | 11.6 bit            | 11.5 bit            | 8-10 bit           |

| Samples               | 256               | 48 rows of 512             | 256                  | 2048        | 1024-12288          | 1024-8192           | 64                 |

| Clock                 | 33 MHz            | 33 MHz                     | 66 MHz               |             | 20 MHz              | 15amp/2048          | 60 MHz             |

| Max late icy          |                   |                            | 5ms                  |             | 0.6 ms              |                     |                    |

| hp at B affers        |                   | TIA (SkOhm galt)           | Yes                  | No          | No                  | No                  | Yes                |

| Differential inputs   | No                | Pse∉do-diff                | Yes                  |             | Yes                 | Yes                 | Pse∎dodhff         |

| input impedance       | 500 kms Ext       | 30-700 kms adjustable      | > 10 MQ.km           |             |                     | 7-11pF              |                    |

| Readoutclock          |                   | 1 G Hz Wilkins on          | 16 MHz               |             | 33 MHz              | 33 MHz              | 60 MHz             |

| Readout time          | 150µs             | 512ps                      | < 2 μs               |             | 3016 °<br>Lasamples | 3016 °<br>Lasamples | < 1 µ3             |

| Locke dide lays       | ExtDAC            | ExtOLL                     | 1) DLL               |             | ExtPLL              | JUT P LL            |                    |

| On-chip ADC           | Yes               | 1 GHz Wikhson              | No                   |             | No                  | No                  | Yes                |

| RAW sim ultaneous     |                   | Yes                        | No                   |             | No                  | Yes                 | No                 |

| Power <i>i</i> c)     | 50mW              | 20mW/s ample<br>0.2W/read  | 150 m.W              |             | 1-13mW              | 2-20mW              |                    |

| Dynamic range         |                   | 1mV/1V                     | 0.65m V-2V           |             | 0.35m V/1.1V        | 0.35/1V             | 1V                 |

| Xtalk                 | Average<br><< 10% | < 0.1%                     | 0.30%                |             | <0.5%               | <0.5%               |                    |

| Sam pilng jitter      |                   | TED                        | 40ps                 |             | 200ps (Ext<br>PLL)  | ExtPLL              | 10ps               |

| Powersupplies         | 2.5V              | 2.5V                       | 0-3.3V               |             | 2.5V                | 2.5 V               | 1.8V               |

| Process               | TSMC 0.25         | TSMC 0.25                  | AMS 0.35             | AMS<br>0.18 | UMC 0.25            | UMC 0.25            | CMOS0.13           |

| Chiparea              | 2.5 mm2           | 12 mm 2                    | 10 mm 2              |             | 25 mm 2             | 25 mm 2             | 1 m m 2            |

| Costchannel           |                   | 500\$/40 10\$/2k           | 15.7 <b>\$</b> /12k  |             |                     | 10-15\$             |                    |

Table 1. State of the art, this proposal. The yellow column is from Gary Varner's group at the University of Hawaii (USA) [12], the light blue from Dominique Breton from the University of Paris-Sud (Orsay) [10] and Eric Delagnes from CEA (Saclay), (France) [11]. The orange column from Stefan Ritt at PSI (Switzerland). [13]. The dark blue is this proposal.

🗉 🗇 🖾 🖌 🔛

94

Sec 1 4/14 At 9.7" Ln 57 Col 1 REC TRK EXT OVR

#### **Front-end Electronics**

■ Wave-form sampling does well- CMOS (!)

#### **Front-end Electronics-II**

## Cartoon of a `frugal' MCP

Put all ingredients together- flat glass case (think TV's), capillary/ALD amplification, transmission line anodes, waveform sampling

TRAY

3,5,09 H.F. R.N.

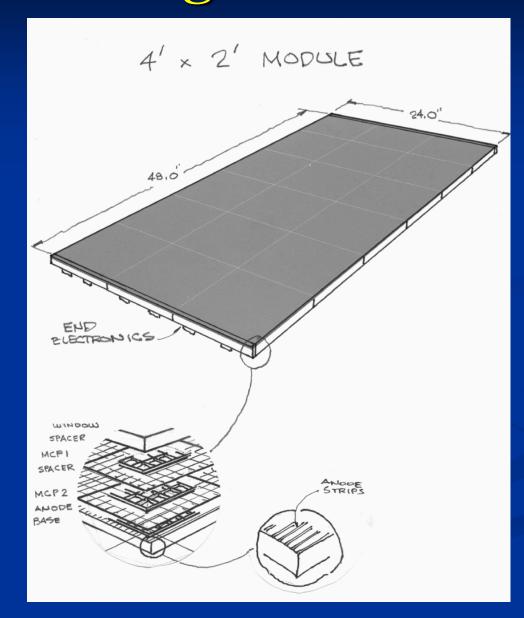

#### Can dial size for occupancy, resolution- e.g. neutrinos 4'by 2'

4/16/2009

## **Plans to Implement This**

#### The Development of Large-Area Fast Photo-detectors April 15, 2009

John Anderson, Karen Byrum, Gary Drake, Edward May, Alexander Paramonov, Mayly Sanchez, Robert Stanck, Hendrik Werts, Matthew Wetstein<sup>1</sup>, Zikri Yusof High Energy Physics Division Argonne National Laboratory, Argonne, Illinois 60439

> Bernhard Adams, Klaus Attenkofer Advanced Photon Source Division Argonne National Laboratory, Argonne, Illinois 60439

> Zeke Insepov Mathematics and Computer Sciences Division Argonne National Laboratory, Argonne, Illinois 60439

> Jeffrey Elam, Joseph Libera Energy Systems Division Argonne National Laboratory, Argonne, Illinois 60439

Michael Pellin, Igor Verycvkin, Hau Wang, Alexander Zinovev Materials Science Division Argonne National Laboratory, Argonne, Illinois 60439

> David Beaulieu, Neal Sullivan, Ken Stenton Arradiance Inc., Sudbury, MA 01776

Mircea Bogdan, Henry Frisch<sup>1</sup>, Jean-Francois Genat, Mary Heintz, Richard Northrop, Fukun Tang Enrico Fermi Institute, University of Chicago, Chicago, Illinois 60637

> Erik Ramberg, Anatoly Ronzhin, Greg Sellberg Fermi National Accelerator Laboratory, Batavia, Illinois 60510

James Kennedy, Kurtis Nishimura, Marc Rosen, Larry Ruckman, Gary Varner University of Hawaii, 2505 Correa Road, Honolulu, HI, 96822

> Robert Abrams, Valentin Ivanov, Thomas Roberts Muons, Inc 552 N. Balavia Avenue, Balavia, IL 60510

Jerry Va'vra SLAC National Accelerator Laboratory, Mento Park, CA 94025

Oswald Siegmund, Anton Tremsin Space Sciences Laboratory, University of California, Berkeley, CA 94720

> Dmitri Routkevitch Synkera Technologies Inc., Longmont, CO 80501

David Forbush, Tianchi Zhao Department of Physics, University of Washington, Scattle, WA 98195

<sup>1</sup> Joint appointment Argonne National Laboratory and Enrico Fermi Institute, University of Chicago

Have formed a collaboration to do this in 3 years. 4 National Labs, 5 Divisions at Argonne, 3 companies, electronics expertise at UC and Hawaii

**R&D-** not for sure, but we see no show-stoppers

4/16/2009

What can LHCb do? Need Serious Simulation of 1-10psec TOF

- Need a list of physics drivers- (e.g J/Psi-eta, pizero-Kzero CP Asym.,...)

What is required rate, occupancy vs radius?

- What resolution is necessary for each analysis?

What is budget, schedule?

So need a serious simulation effort. Are there folks who would work with us on this and vice versa?

# The End-

#### Get position AND time Anode Design and Simulation(Fukun Tang)

Tube Outline 58x58mm Transmission Line- readout both ends—> pos and time Cover large areas with much reduced channel account.

#### Photonis Planicon on Transmission Line Board

Couple 1024 pads to strip-lines with silver-loaded epoxy (Greg Sellberg, Fermilab).

4/16/2009

#### **Front-end Electronics**

■ Wave-form sampling does well- CMOS (!)

#### 4/16/2009

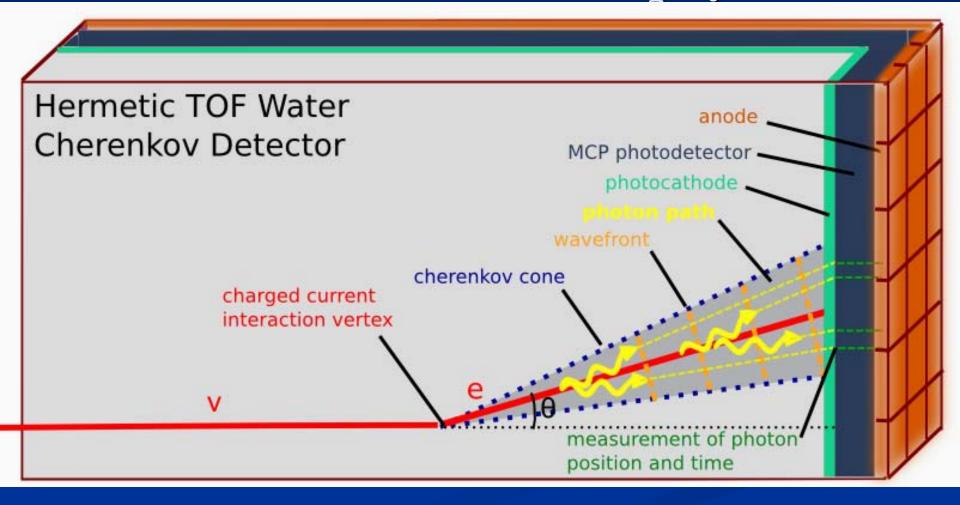

# Application to a water Cherenkov Counter- effect on the physics