# Transmission-Line Readout with Good Time and Space Resolution for Large-Area MCP-PMTs

## Fukun Tang (UChicago)

C. Ertley, H. Frisch, J-F. Genat, Tyler Natoli (UChicago) J. Anderson, K. Byrum, G. Drake, E. May (ANL) Greg Sellberg (FNAL)

- Introduction

- Characteristics of MCP-PMT output signals

- Readout techniques for picoseconds timing measurements

- Transmission-line readout design and simulations

- 40Gsps fast sampling chip design

- Summary & plan

TWEPP 2008, Naxos, Greece, September 15-19 2008

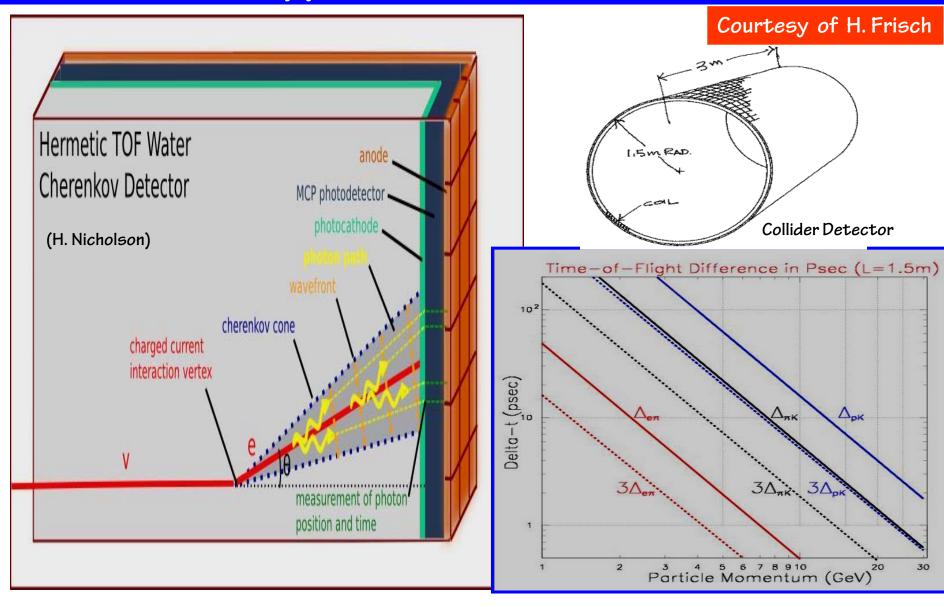

## Introduction: Applications of Time-of-Flight for HEP

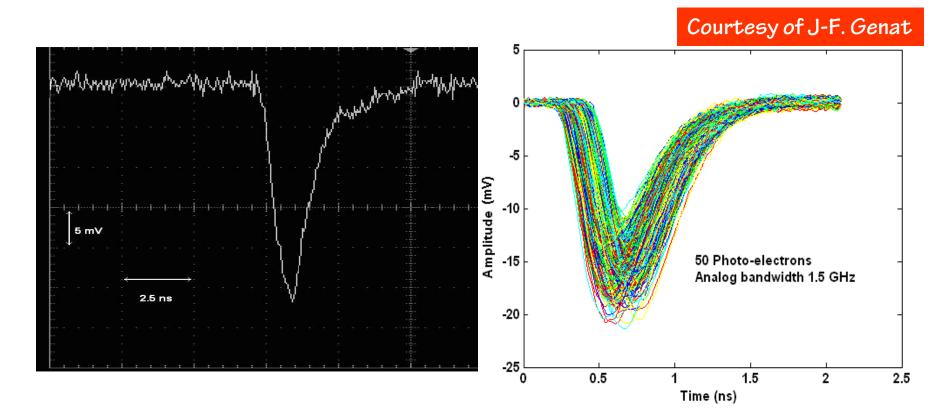

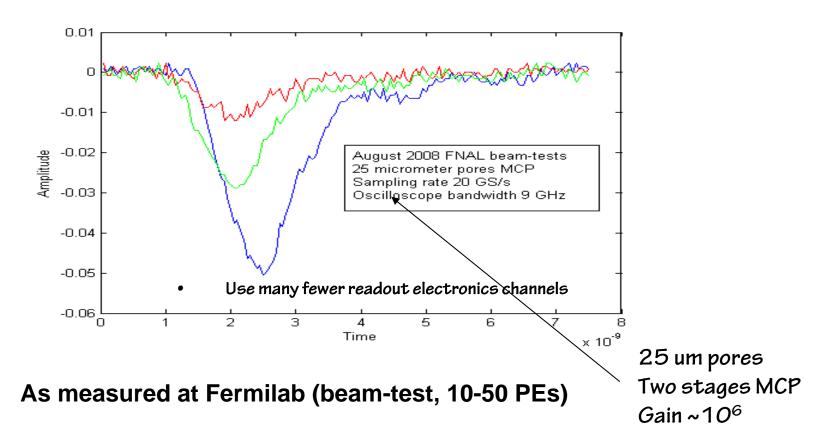

# MCP signals

- Measured (beam-tests)

- Rise-time: 380ps

- 25um pores

Simulation:

- Rise time 200ps (6um pores) →bw=1.75GHz

- Time spread: +/- 125ps, random

- Amplitude spread: 14%, normal

F.Tang

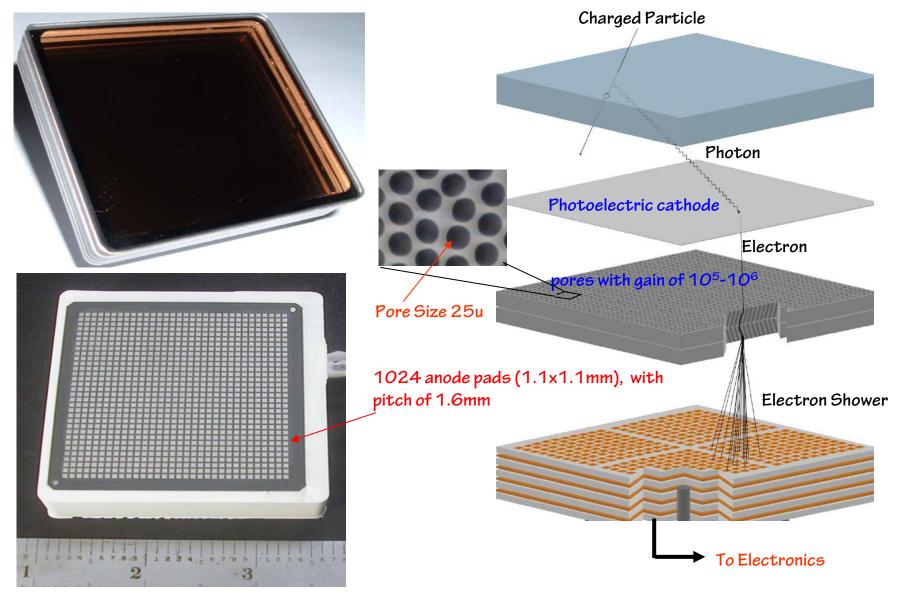

## Introduction: Planacon MCP-PMT Tube & Anode Array

# MCP signals (beam-test)

$I(1PE) = dQ/dt \sim 1.6 \times 10^{-19} \times 5 \times 10^{5} / 250 \text{ ps} = 320 \text{ uA}$ Expect:  $16 \text{ mV} @ 50 \Omega$

# Fast Timing Electronics

### Current techniques:

- Leading edge + TDC/ADC

- Constant fraction + TDC/ADC

- Zero-crossing + TDC

- Double / multiple thresholds + TDC/ADC

- Pulse sampling and reconstruction

The most favorable method is <mark>sampling</mark>, particularly in the case of few Photo-electrons. Samples as effective for timing as steep signal slope and large signal/noise ratio

Use today existing sampling chips in first step: Hawaii, PSI, Saclay/Orsay (sampling rate @2-5 GHz, 10-13 bits)

- Derive accurate time and charge using digital signal processing

- Resolve pile-up, transmission line readout ambiguities

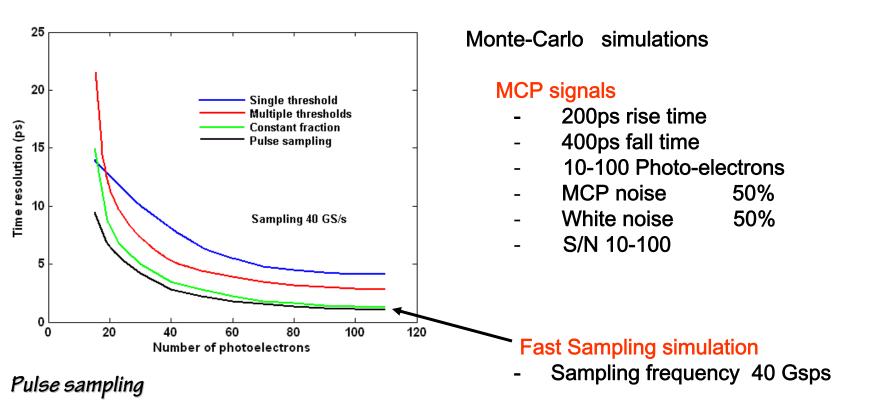

# Fast timing simulations

Assume 1.5 GHz analog bandwidth:

100 samples taken at 10-40 Gsps allow reconstructing time to a few picoseconds and charge to one per cent.

- Better time resolution compared to CFD particularly at low PEs,

- Records the full pulse information

F.Tang

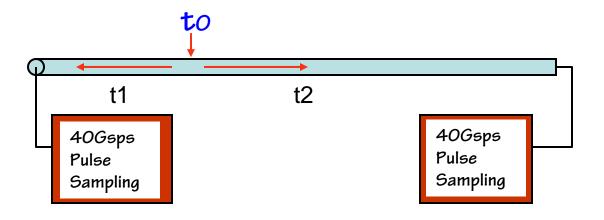

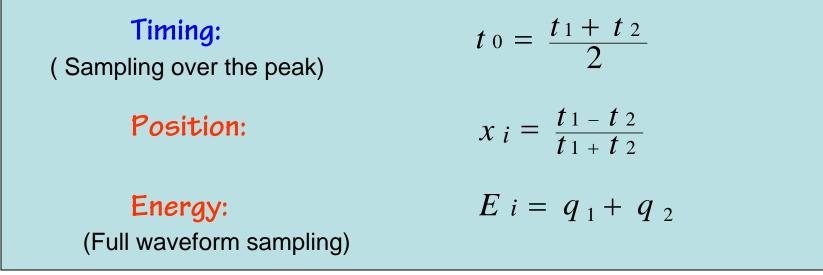

# Proposed Transmission –line and Fast Sampling Readout for Planacon MCP-PMT

- Why use transmission-line readout?

- Advantages of transmission-line and fast sampling techniques:

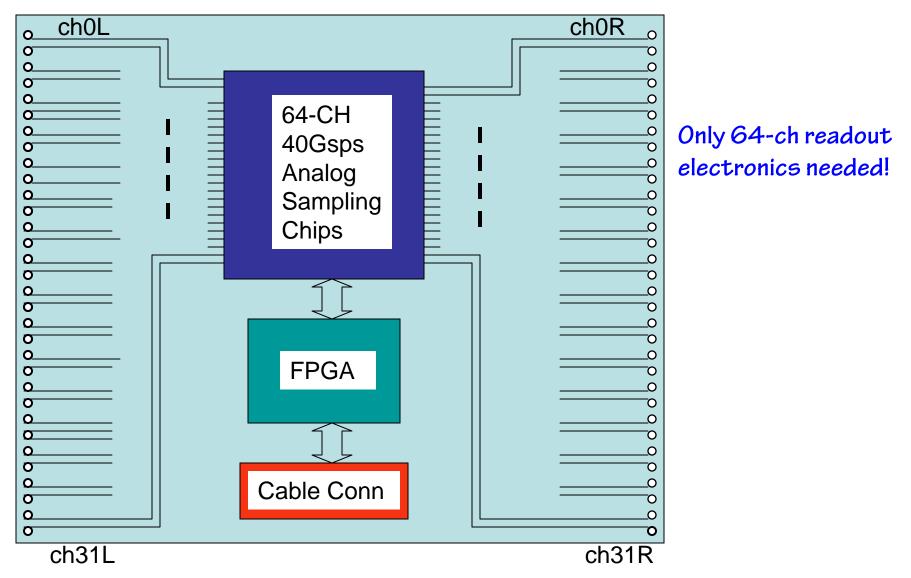

- Use many fewer readout channels (1024 down to 64 channels)

- Readout timing, position and energy information

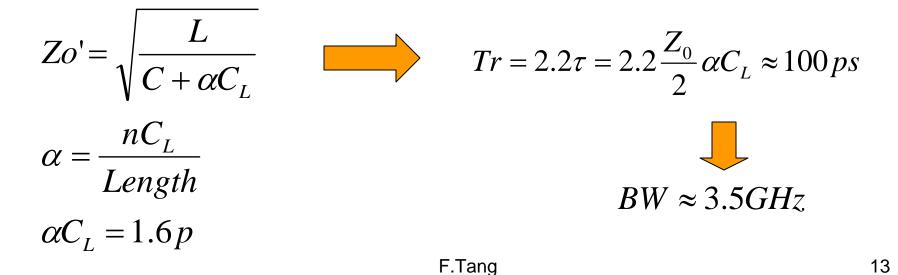

- Good transmission-line bandwidth (up to 3.5GHz)

## Principle of Transmission-line Anode Readout

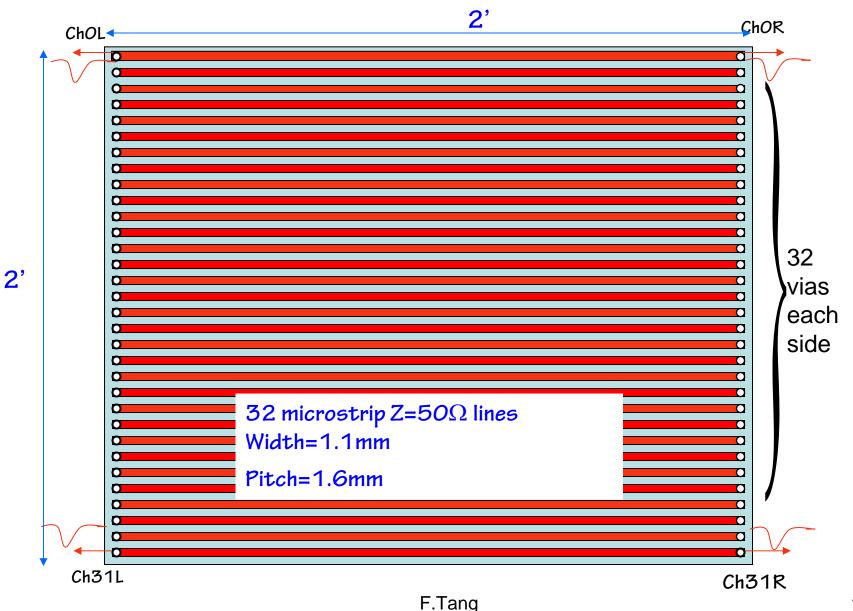

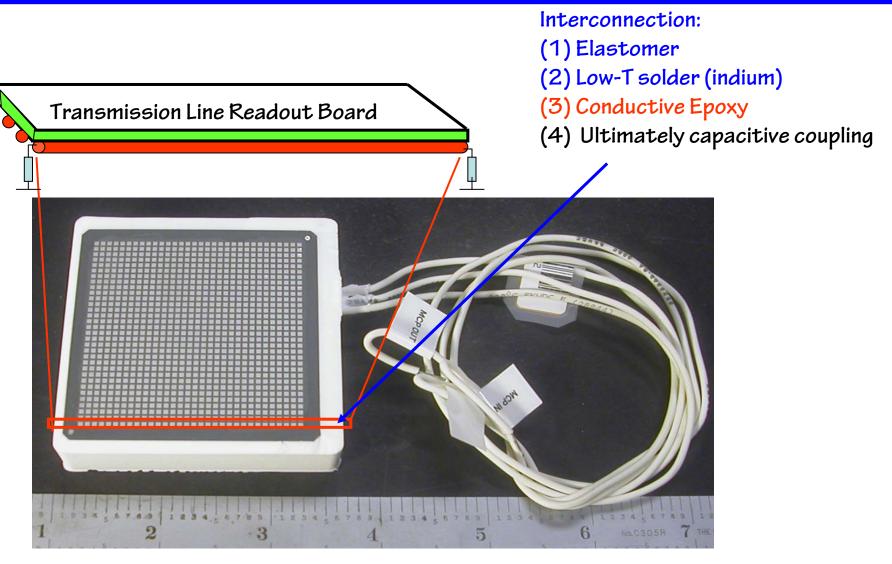

## Proposed Transmission-line Anode Board (top view)

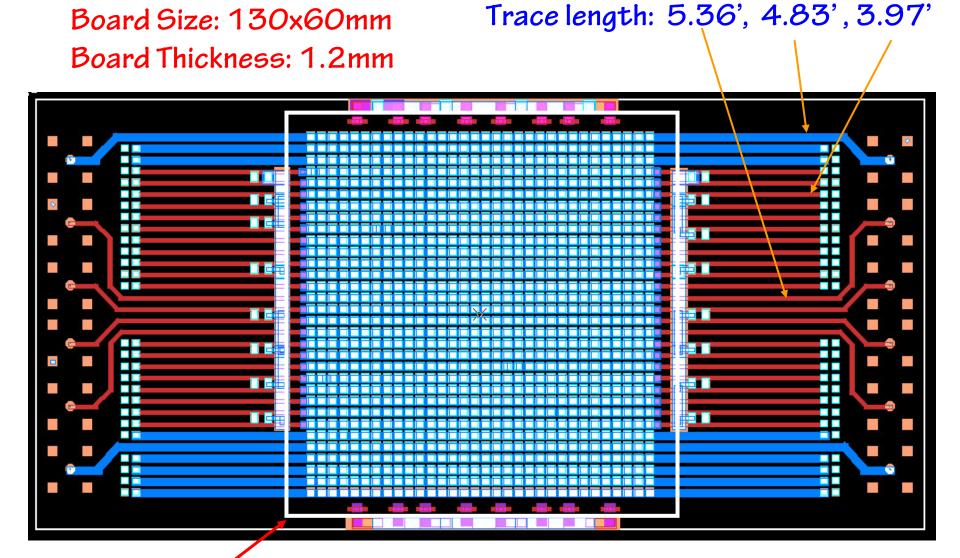

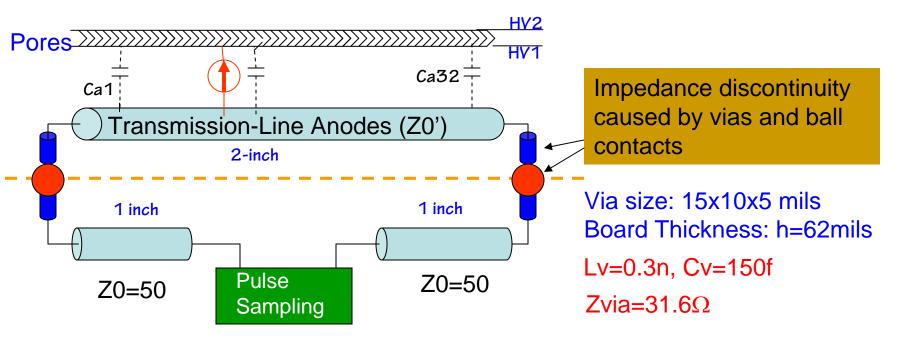

## Prototype Transmission-line Readout Board Design and Simulations Based on Commercial 2'x2' 1024-Anode Tube

### Layout of Prototype Transmission-line Readout Board

Tube Outline 58x58mm

F.Tang

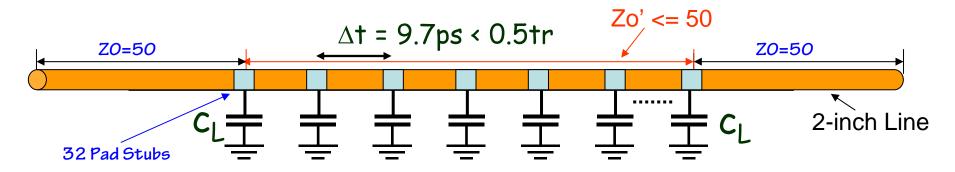

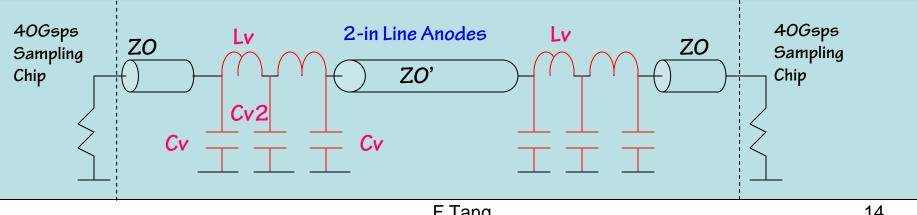

## Bandwidth Analysis for Transmission-line Readout

Simplified model with the transmission-line readout board attached to MCP-PMT:

Equal distributed 32  $C_L$ =100f along 2-inch line, It reduces impedance to Zo', However, it also reduced the BW.

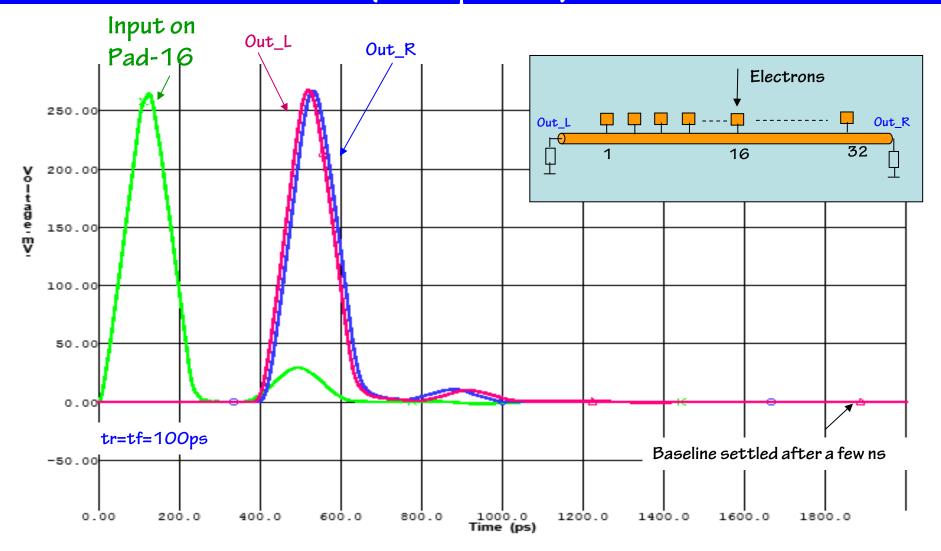

# Outputs on Each End of Transmission-line with Stub Anodes (hit at pad-5)

Electrons Input Force: Tr=tf=200ps Out\_R Out\_L р Ф OSCILLOSCOPE Design file: MCP.FFS Designe 32 1 5 HyperLynx-V7.7 Output on left\_end (t1) 1000.0 800.0 600.0 400.0 200.0 0.00 -200.0 Reflection caused by -400.0 Output on right\_end (t2) impedance mismatch and discontinuity -600.0 -800.0 600.0 0.00 200.0 400.0 800.0 1000.0 1200.0 1400.0 1600.0 1800.0 Time (ps)

Voltage · EV

Date: Monday Mar. 3, 2008 Time: 16:50:21 Show Latest Waveform = YES, Show Previous Waveform = YES

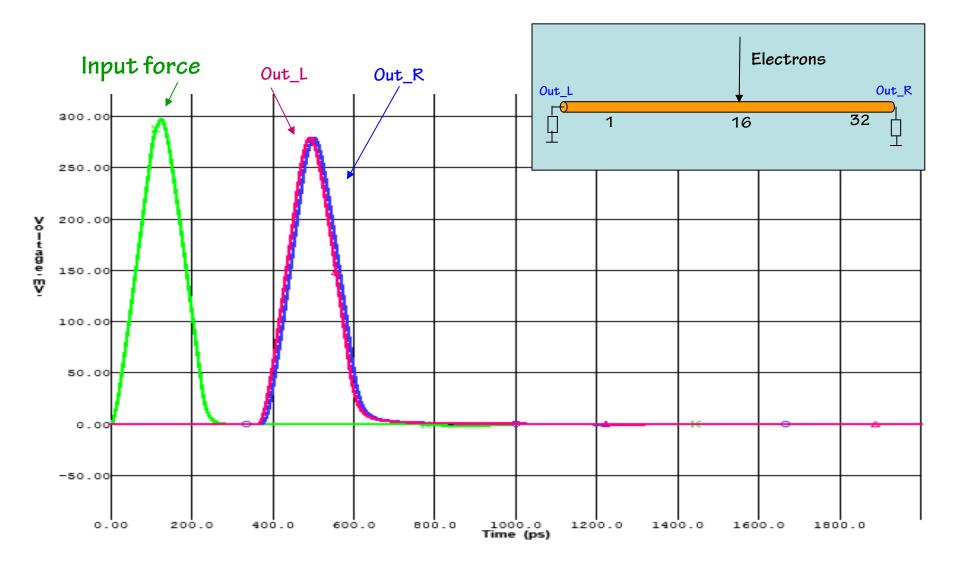

# Outputs on Each End of Transmission-line with Stub Anodes (hit at pad-16)

### Outputs on Each End of Transmission-line without Stub Anodes (hit at the same position as pad-16)

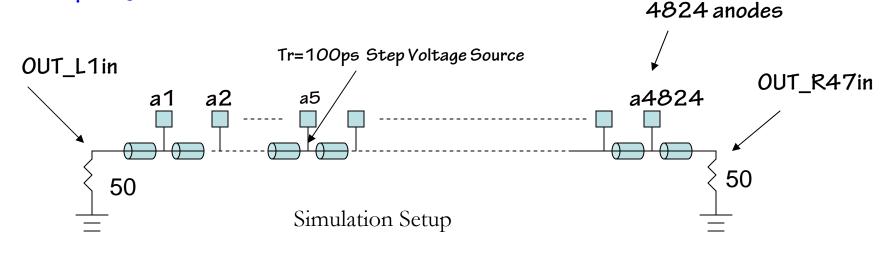

## Simulation with Transmission-Line Anode up to 48-inches

Simulation Goal:

To understand analog signal bandwidth vs. the length of transmission-line for MCP anode design.

### System Setup:

The simulation model is extracted from a board layout. The transmission-line impedance Z=50 ohms, the length is 48-inch with 4824 tapped anodes which induce 100f capacitance each.

#### Input Force:

A step voltage input force with a rise time of 100ps, an amplitude of 1.4Vexcites the line at the point 1-inch from the left end.

#### Outputs:

Comparing the rise time between both ends of the line.

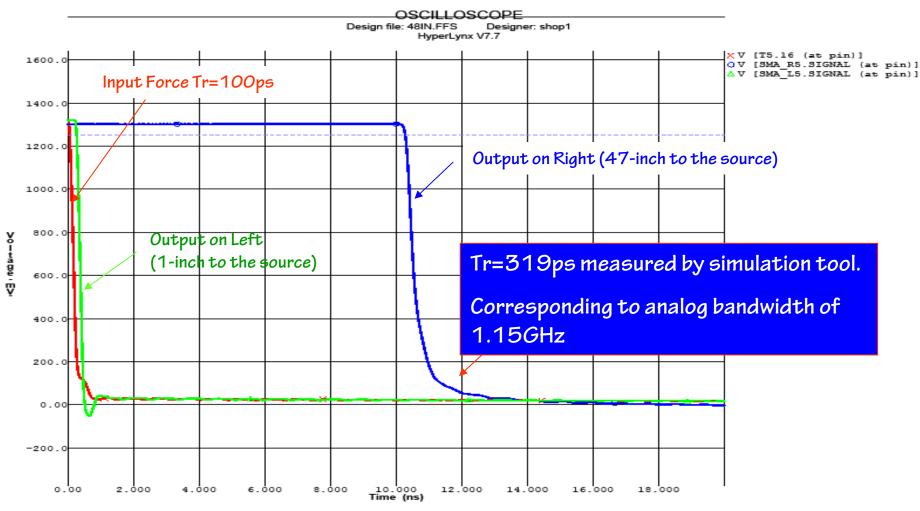

## Responses on each end of 48-inch transmission-line (Hit at the position 1-ch to the left)

Date: Thursday Jul. 24, 2008 Time: 9:24:08 Show Latest Waveform = YES, Show Previous Waveform = YES

## Conceptual Design of Transmission-line and Fast Sampling Readout Electronics

## Fast sampling chip at UChicago

- Technology: IBM 8RF DM 130nm CMOS design kit from CERN

- Key numbers of UChicago Fast Sampling Chip

- -- 40 GHz sampling

- -- 1-2 GHz analog bandwidth

- -- 8-10 bit ADCs

- -- Self/Global trigger

- -- Time Stamping

- -- Readout protocols

- 🕏 Work in Progress:

- Unity gain input buffer design(1-2GHz BW)

- Analog bandwidth is 1.6 GHz (-3dB) using current mode amplifier has been achieved (pre-layout).

To be improved:

Tuning input impedance of 200  $\Omega$  to 50  $\Omega$  with

the IBM130nm CMOS DM (analog RF) process when available.

--Extend analog bandwidth as far as possible, if input buffer can not meet the requirement.

-Sampling timing generator design

-Sampling cells and ADCs: Experience from Orsay/Saclay, Hawaii and PSI.

# Expect 2-3ps timing resolution with MCP signals

# Summary

### Advantages:

- Use many fewer readout electronics channels

- Readout timing, position and energy information

- Good signal bandwidth

- Easy to match impedance all the way to the chip input

- Plans (short and long term)

- Prototyping transmission-line readout with laser stand and 40Gsps scope (in few weeks)

- Transmission-line readout with two LAB2 or two DRS4 Chips (possibly 2x interleaving?) (in few months)

- Development of 40Gsps sampling chip for large scale detectors ---2-ch demonstration chip with IBM 8RF 0.13u CM0S (year 1) --- 32/64-ch chip (year 2)

- Built-in transmission-line anode design and simulation (need to work with tube designers)