# PSEC4 waveform sampler & Large-Area Picosecond Photo-Detectors readout electronics

12-March 2014 : Workshop on Picosecond Photon Sensors, Clermont-Ferrand Eric Oberla

#### HIGH ENERGY PHYSICS THE UNIVERSITY OF CHICAGO

## Overview

- PSEC4 waveform sampler/digitizer

- The Large-Area Picosecond Photo-Detectors (LAPPD) glass package

- DAQ system : readout of large area microchannel plates

- Plans for PSEC5

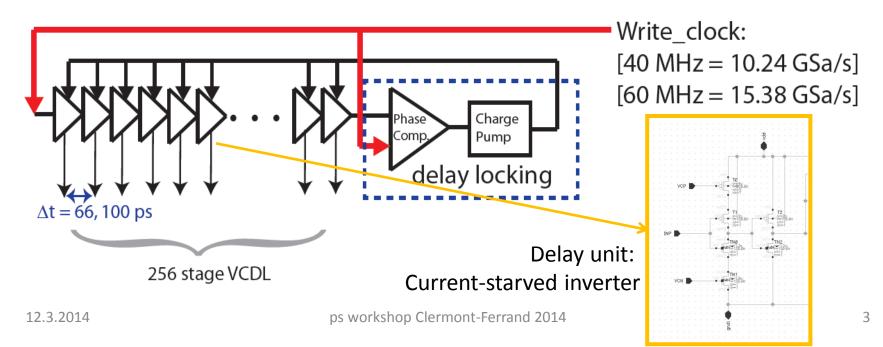

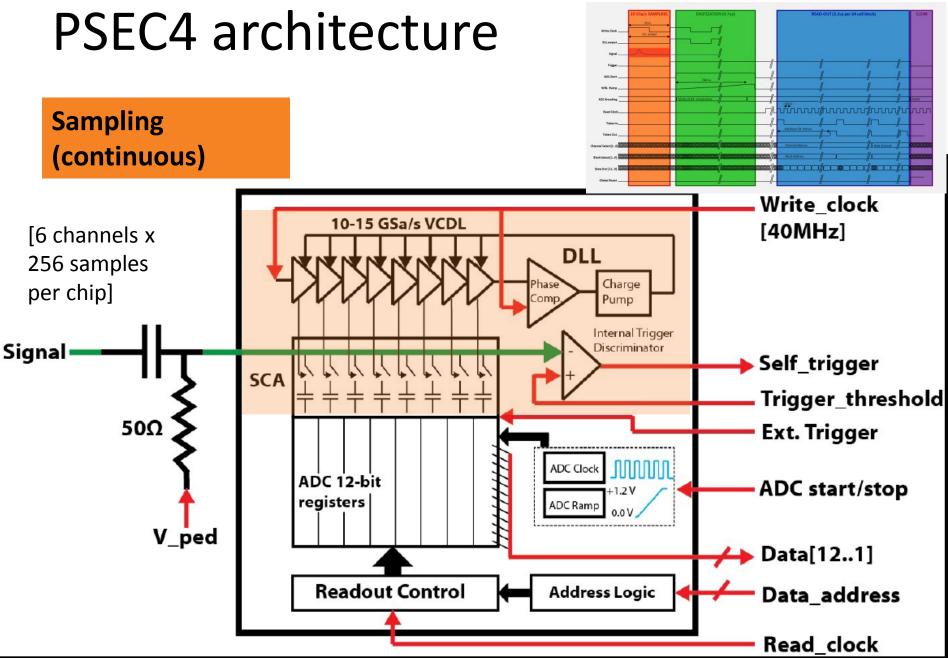

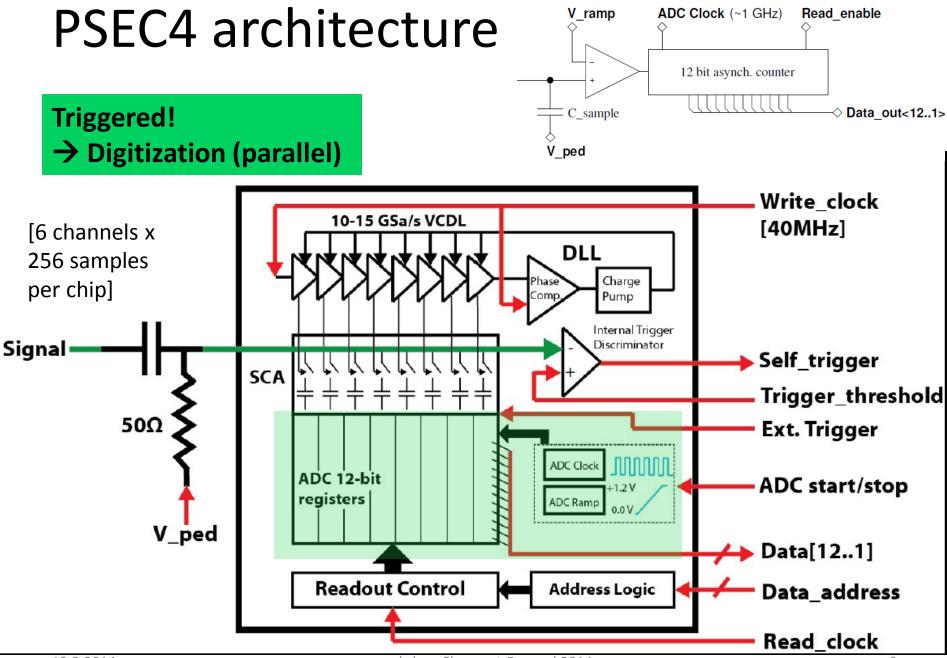

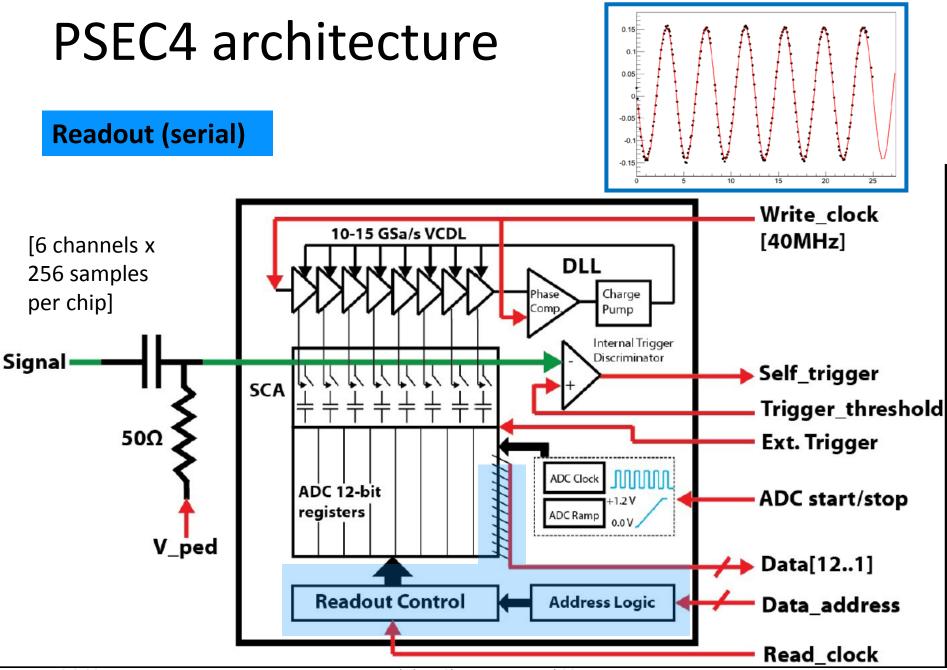

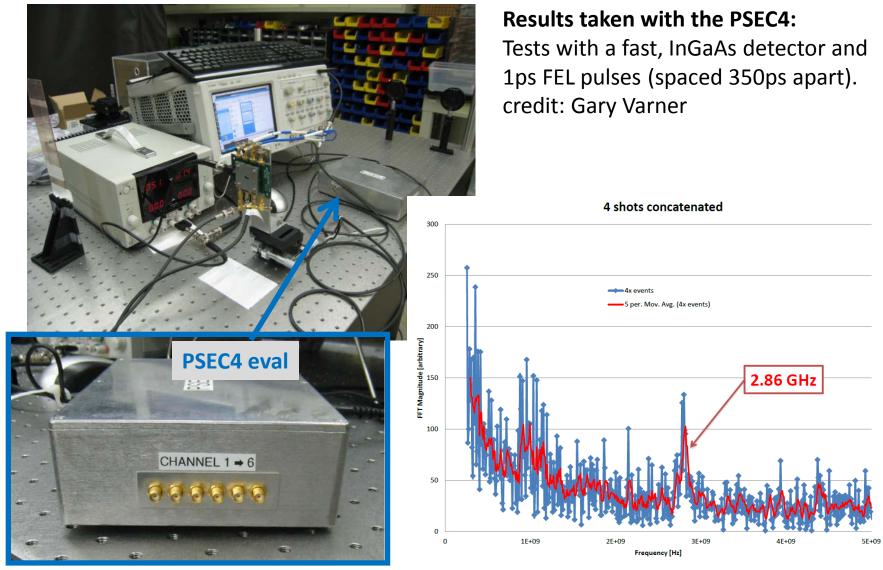

## $\mathsf{PSEC4}: 0.13 \ \mu m \ \mathsf{CMOS}$

- 10-15 GSa/s Switched Capacitor Array (SCA) sampling

- Up-convert low frequency (~10's MHz) clock to multi-GHz using tapped voltage-controlled delay line (VCDL):

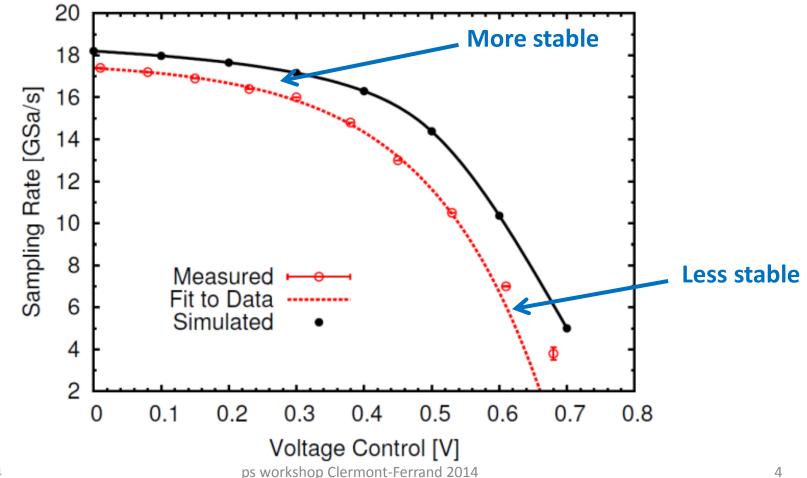

# Sampling Rate

- Sampling rate locked on-chip

- ~Small recording window [25 ns when sampling at 10.24 GSa/s]

ps workshop Clermont-Ferrand 2014

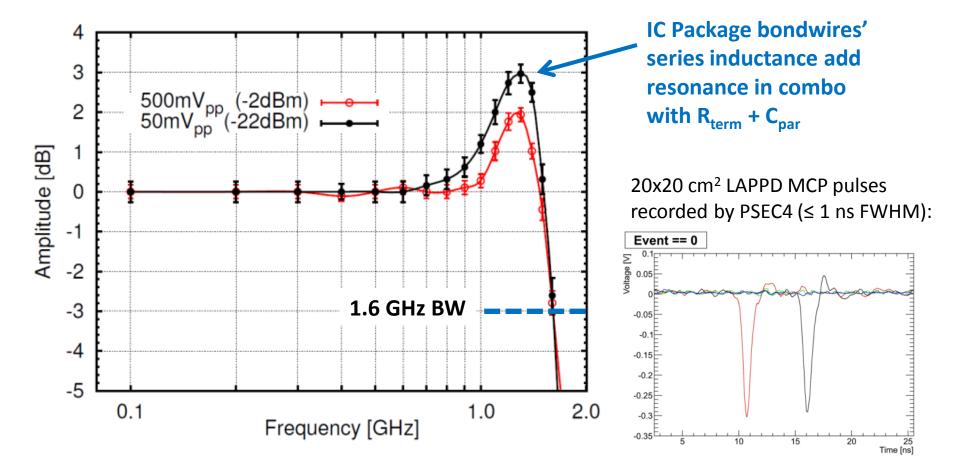

## Analog Bandwidth

Preserve the rise-times of fast (photo)detectors on chip: maximize analog bandwidth

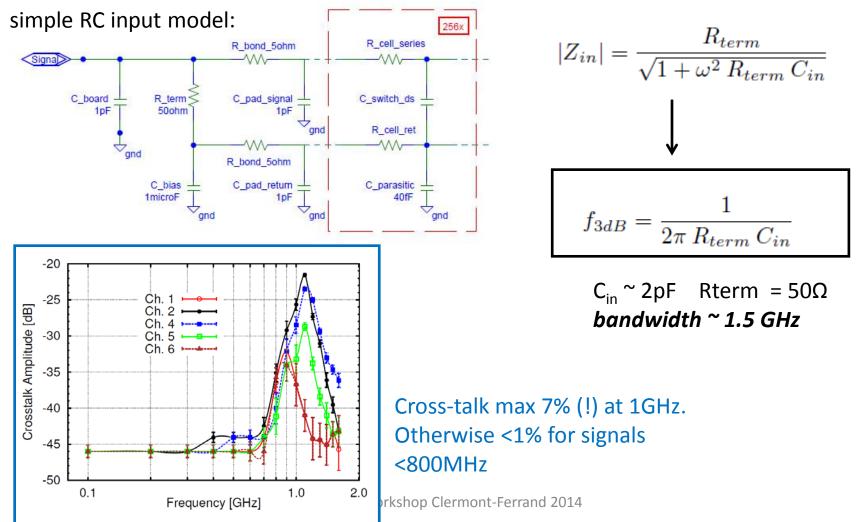

## Analog Bandwidth + xtalk

• Bandwidth limited by parasitic input capacitance (C<sub>in</sub>), which drops the input impedance at high frequencies:

9

## Analog Bandwidth

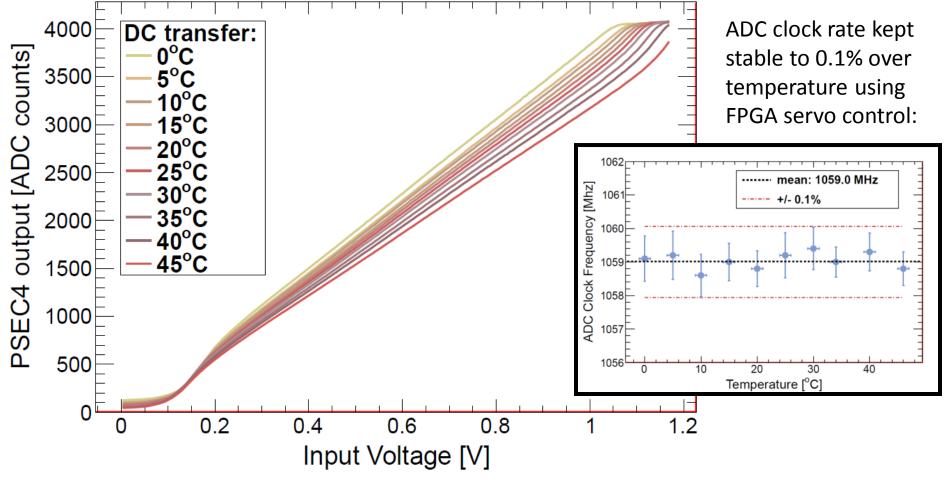

### Ramp-compare ADC linearity + stability

- Un-calibrated integral non-linearity 0.15% over 750 mV range

- Full 1 V signal voltage range after calibration (DC noise RMS ~0.7 mV)

- Some temperature dependence observed:

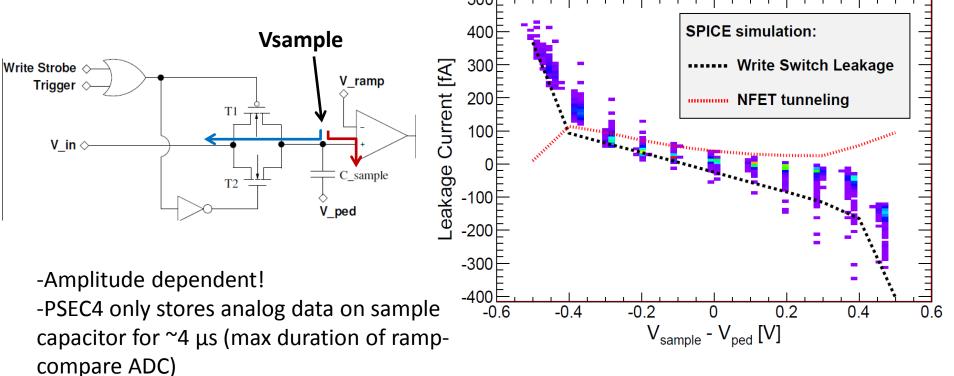

### Sample Leakage

- Sub-threshold conduction through write switch (T1/T2)

- Gate-oxide tunneling through NFET at comparator input

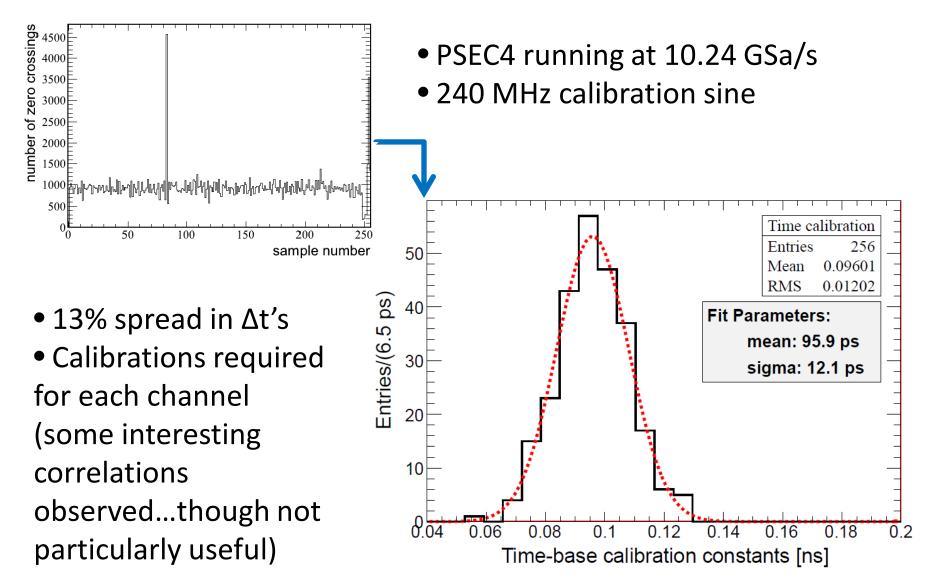

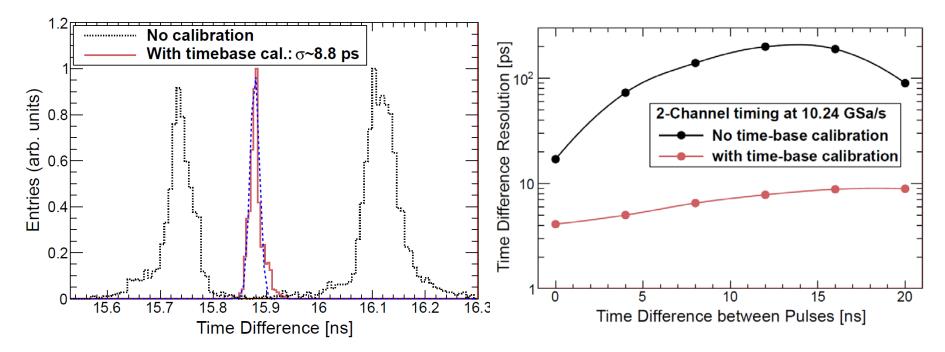

### **Timing calibration**

- Overall PSEC4 time-base locked on-chip

- Individual time-steps are not uniform due to process variations

- Employ a 'brute force' method for calibrating PSEC4's

256 sample time steps:

- 1) Record ~100K sine waves with period T<sub>input</sub>

- 2) Measure average # of zero crossings per cell

- 3) With enough statistics, can extract Δt for each timestep:

$$<\Delta t > = T_{input *} < N_{zero} > / (2*N_{events})$$

Also, a novel method that didn't quite work for PSEC4:

K. Nishimura, A. Romero-Wolf, "A Correlation-Based Timing Calibration & Diagnostic Technique for Fast Digitization ASICs", Physics Procedia 37 (2012) 1707-1714.

### Timing calibration : example

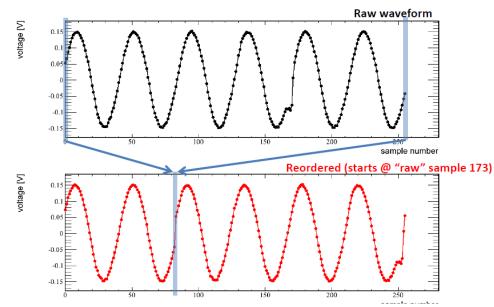

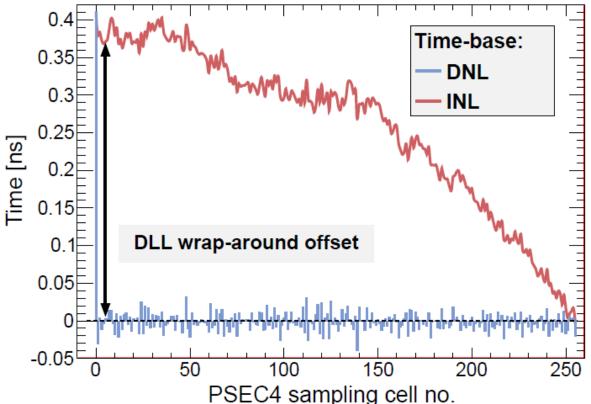

# Timebase DNL/INL

• PSEC4 'wraparound' feature causes first time step to be ~400 ps

known gap at wraparound point between samples

255 and 0

necessary to

reorder waveforms

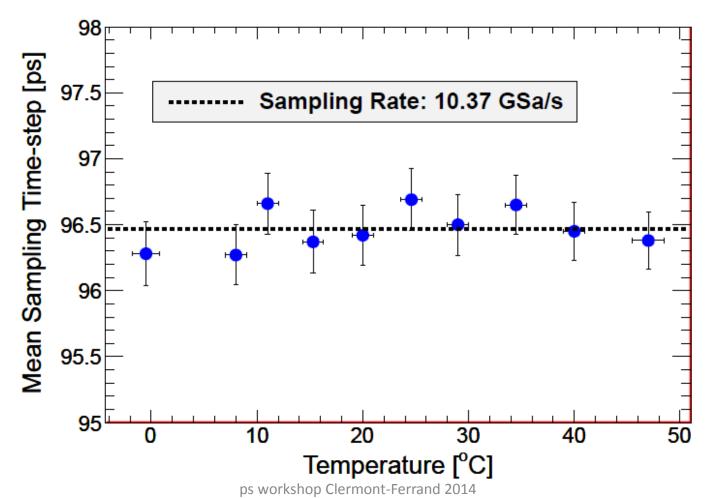

## **Temperature stability**

As expected, PSEC4 DLL keeps effective sampling rate fairly stable over temperature

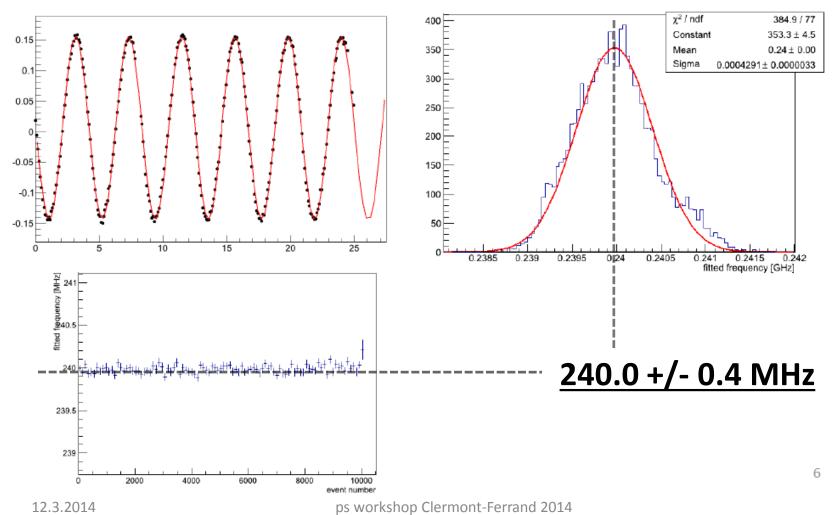

## Timing calibration : verification

- (1) fitting for frequency

- Apply Δt values to another 240 MHz data set, fitting sine waves

- Good fit qualities and stable over events

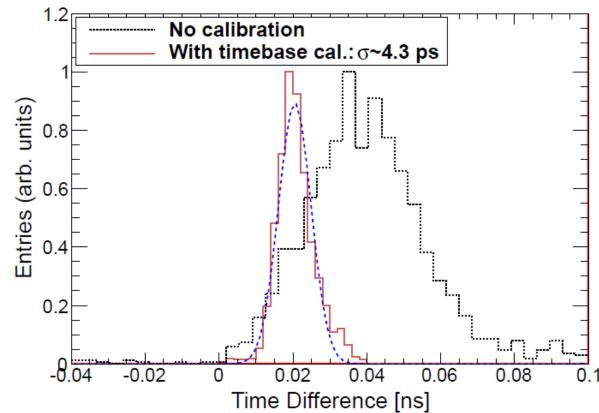

### Timing calibration : verification

- (2) measure 2-channel timing

- Generate ~2 ns FWHM Gaussian pulse, split, and inject into 2 channels of PSEC4

- Apply voltage and time calibrations. Fit pulse rising edge (~10 points) and extract time difference. No other data processing

### Timing calibration : verification

- (2) measure 2-channel timing

- Apply voltage and time calibrations. Fit pulse rising edge (~10 points) and extract time difference. No other data processing

- Measuring timing across PSEC4 recording window. Consistently better than 9 ps.

| Parameter              | Value              | Comment                                                                   | - |  |

|------------------------|--------------------|---------------------------------------------------------------------------|---|--|

| Channels               | 6                  | die size constraint                                                       |   |  |

| Sampling Rate          | 4-15  GSa/s        | servo-locked on-chip                                                      |   |  |

| Samples/channel        | 256                | 249 samples effective                                                     |   |  |

| Recording Buffer Time  | 25  ns             | at 10.24 GSa/s                                                            |   |  |

| Analog Bandwidth       | $1.5~\mathrm{GHz}$ |                                                                           |   |  |

| Crosstalk              | 7%                 | max. over bandwidth                                                       |   |  |

|                        | <1%                | typical for signals $< 800 \text{ MHz}$                                   |   |  |

| Noise                  | $700 \ \mu V$      | RMS (typical). RF-shielded enclosure. After calibration.                  |   |  |

| DC RMS Dynamic Range   | 10.5 bits          | 12 bits logged. Linearity calibration for each cell.                      |   |  |

| Signal Voltage Range   | 1 V                | after linearity correction                                                |   |  |

| ADC conversion time    | $4 \ \mu s$        | max. 12 bits logged at 1 GHz clock speed                                  |   |  |

|                        | 250  ns            | min. 8-bits logged at 1 GHz                                               |   |  |

| ADC clock speed        | $1.4~\mathrm{GHz}$ | max.                                                                      |   |  |

| Readout time           | $0.8n~\mu { m s}$  | <i>n</i> is number of 64-cell blocks to read $(n = 24$ for entire chip)   |   |  |

| Sustained Trigger Rate | 50  kHz            | max. per chip. Limited by $[ADC \text{ time} + \text{Readout time}]^{-1}$ |   |  |

| Power Consumption      | 100  mW            | max. average power                                                        |   |  |

| Core Voltage           | 1.2  V             | $0.13 \ \mu m$ CMOS standard                                              |   |  |

|                        |                    |                                                                           |   |  |

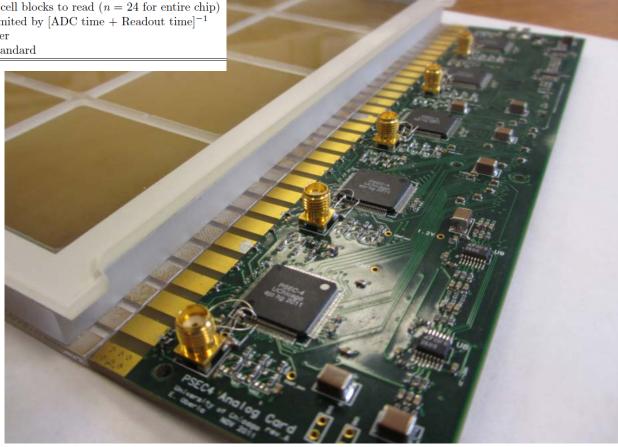

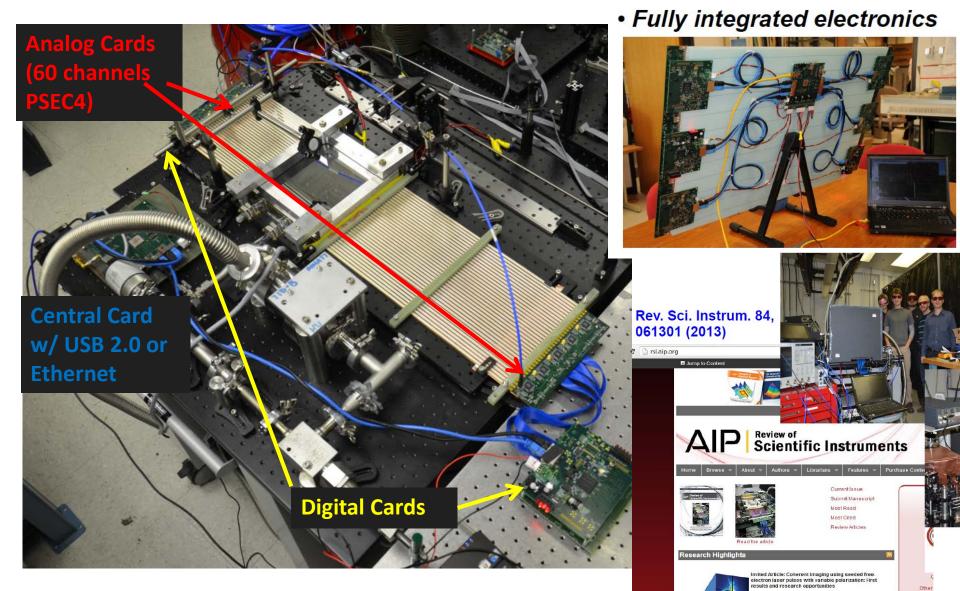

## PSEC4-based DAQ

At the moment: PSEC4 is the baseline readout ASIC for the glass package LAPPD MCP

12.3.2014

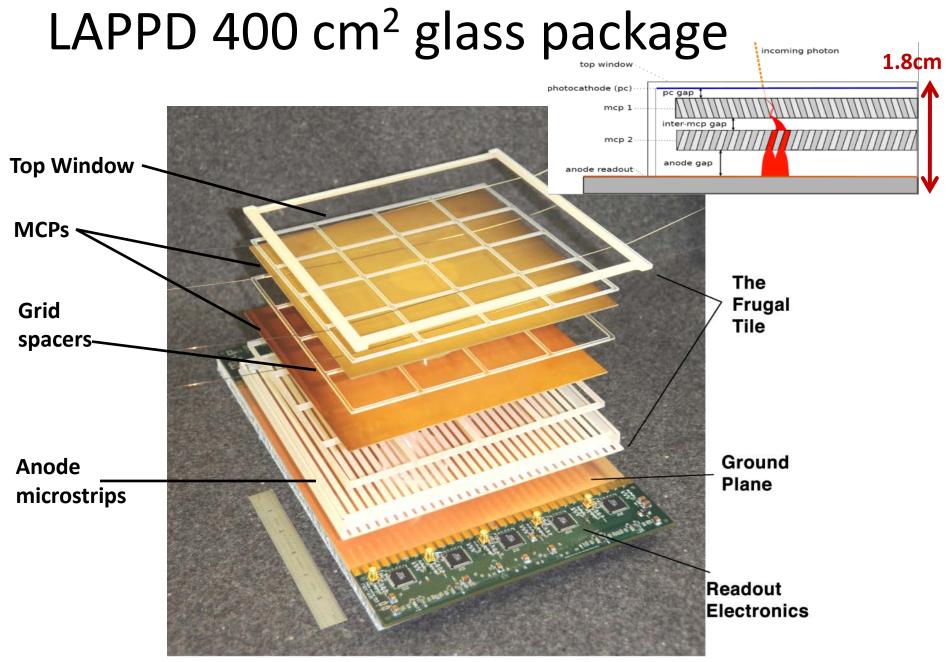

The Frugal Tile - Detector Assembly

#### The 400 cm<sup>2</sup> glass package: **HV** distribution **High Voltage distribution** is embedded in the internal stack-up using ALD grid spacers -HV **Top Window** Photocathode **MCP 1** MCP2 AA Microstrip А Α А A • • • Α Anode ..... Far end anode readout **ξ 50Ω** Near end anode readout 50Ω 22

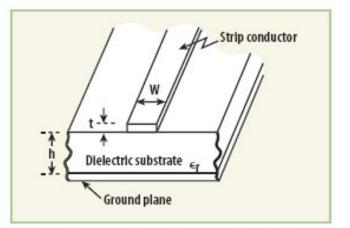

## 400 cm<sup>2</sup> glass package: Microstrip Anode

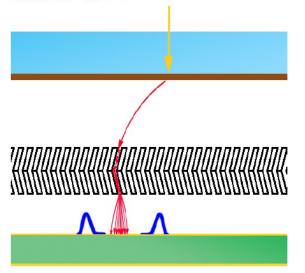

After final amplification, the electron cloud is accelerated towards the anode, inducing EM waves that propagate in both directions along transmission line.

### NIMA 711, (2013) 124-131

1. Microstrip transmission lines consist of a strip conductor and a ground metal plane separated by a dielectric medium.

## 400 cm<sup>2</sup> glass package: Microstrip Anode

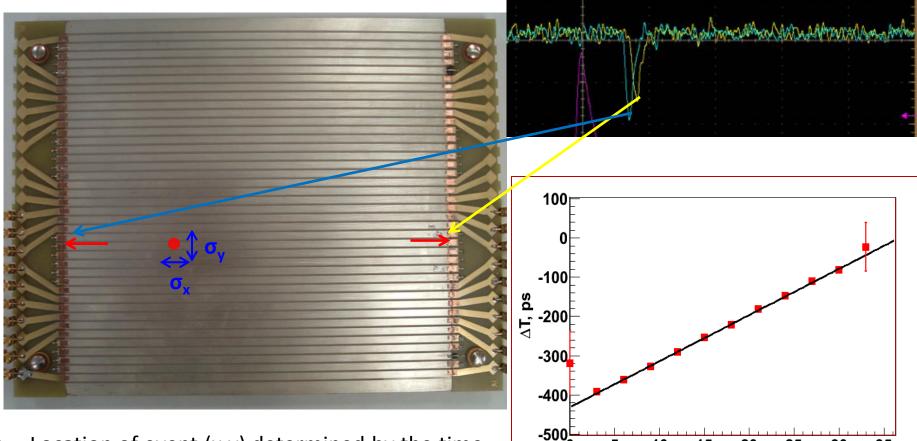

- Location of event (x,y) determined by the time difference of signal on two ends (x) and the charge-centroid of adjacent strips (y).

- Efficient use of electronics channels.

5

10

33mm MCP position scan:

V<sub>prop</sub> ~ 2/3c along stripline

15

20

X, mm

25

30

35

12.3.2014

ps workshop Clermont-Ferrand 2014

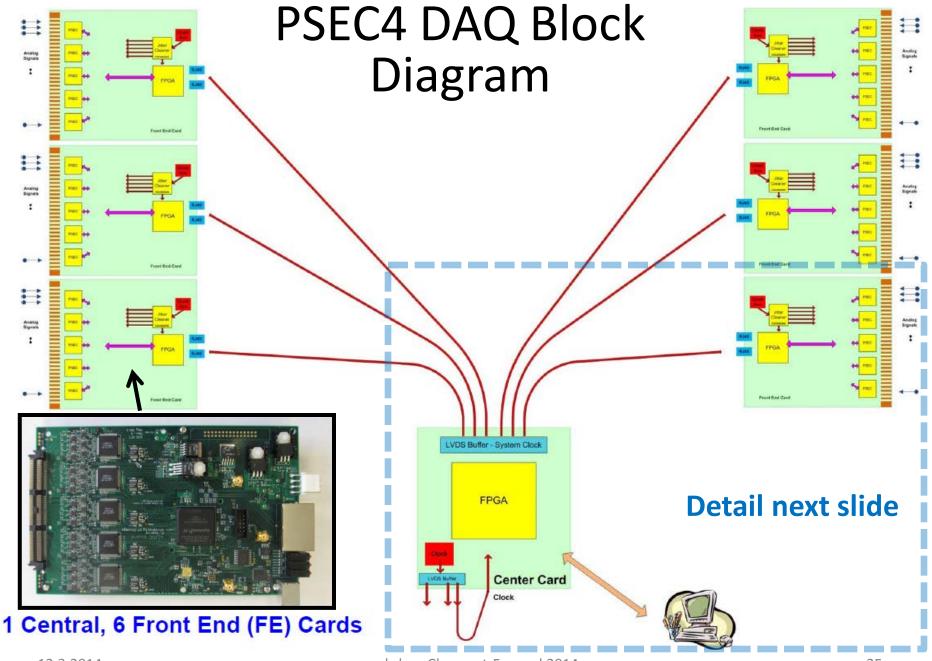

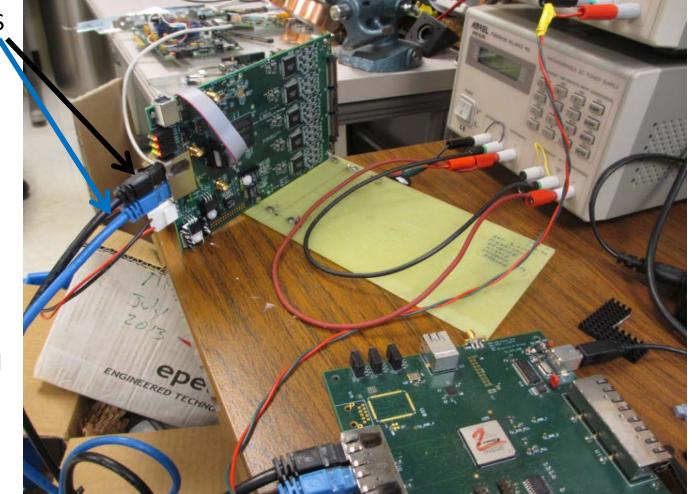

### PSEC4 DAQ: more detail Central card <-> Front-end card communication

- Eight 800 Mbps LVDS pairs

- Data, clock , trigger, configuration

- Front-end card houses 5 PSEC4 chips (30 channels)

- Each front-end card houses jitter cleaner that cleans system clock and distributes to PSEC4s

- Newest board revision has optional mezzanine plug-in for adding a gain stage

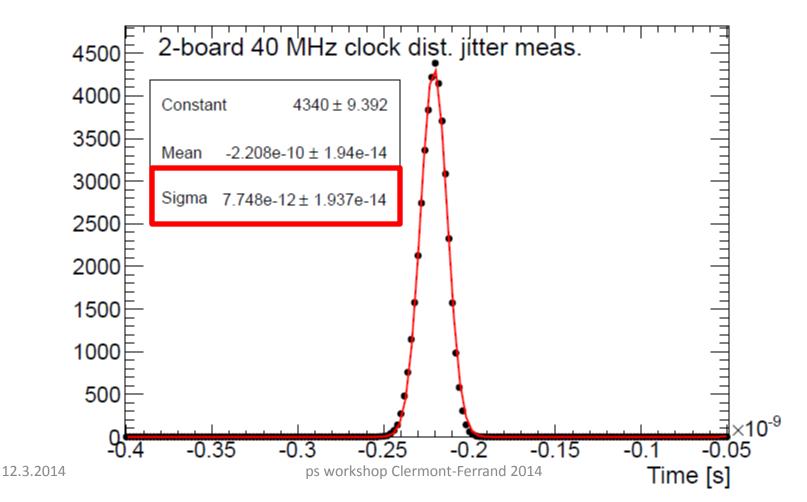

### PSEC4 DAQ: more detail

Clock syncing between front-end boards

- Crucial system parameter: chip and system time resolution require precision clock

- ~7-8 ps clock jitter between boards 'out-of-box'

- Still much room to improve performance of jitter cleaner chip (TI CDCE62005)

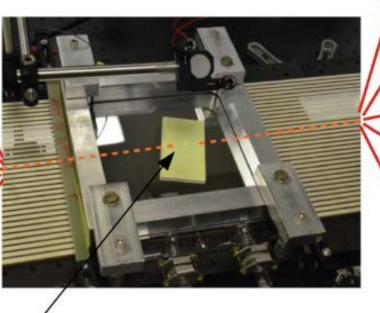

### LAPPD Demountable System Testing @ APS

### First generation LAPPD glass package readout

ps workshop Clermont-Ferrand 2014

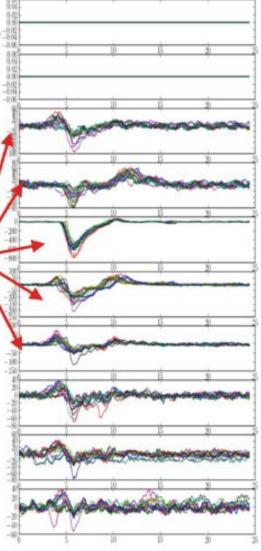

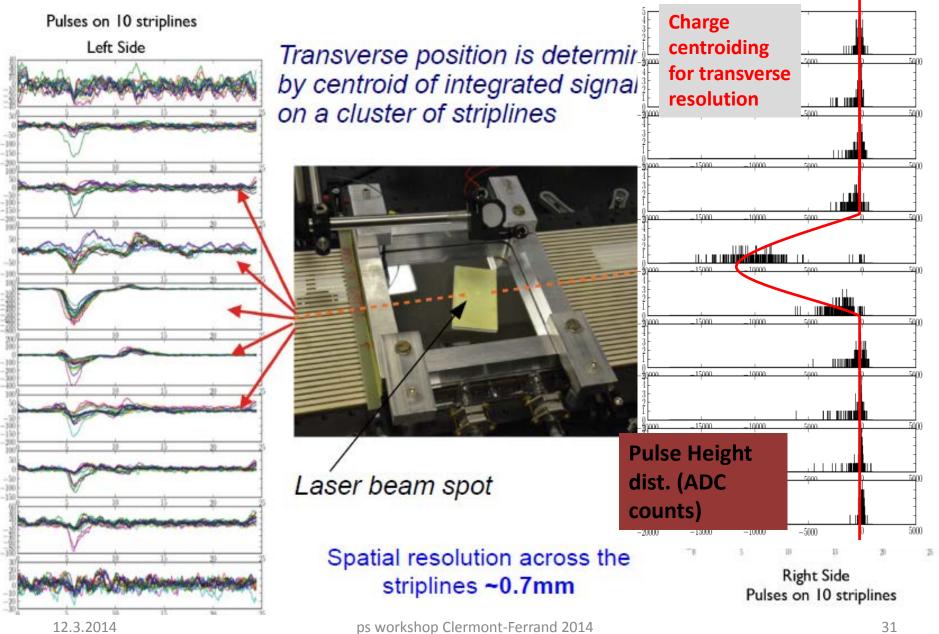

### Position and time reconstruction using PSEC4 pulse recording

Pulses on 10 striplines

Left Side

12.3.2014

Transverse position is determined by centroid of integrated signal on a cluster of striplines

Laser beam spot

## Spatial resolution across the striplines ~0.7mm

Right Side Pulses on 10 striplines

ps workshop Clermont-Ferrand 2014

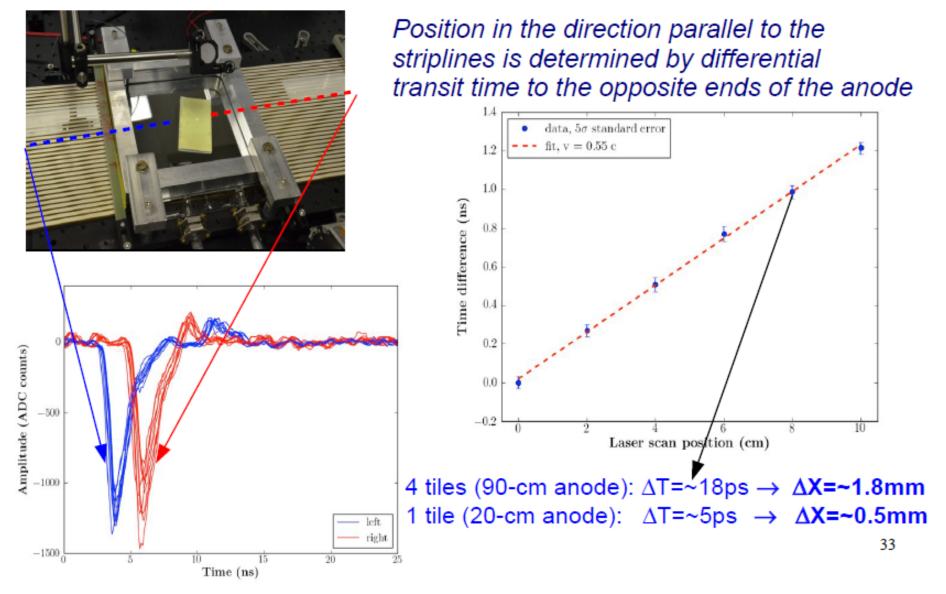

### Position and time reconstruction using PSEC4 pulse recording

12.3.2014

### Position and time reconstruction using PSEC4 pulse recording

B. Adams, A. Elagin, H. Frisch, R. Obaid, E. Oberla, A. Vostrikov, R. Wagner, M. Wetstein, "Measurements of the Gain, Time Resolution, and Spatial Resolution of a 20x20 cm<sup>2</sup> MCP-based Picosecond Photo-Detector", Nucl. Instr. Meth. A (2013), http://dx.doi.org/10.1016/j.nima.2013.07.091.

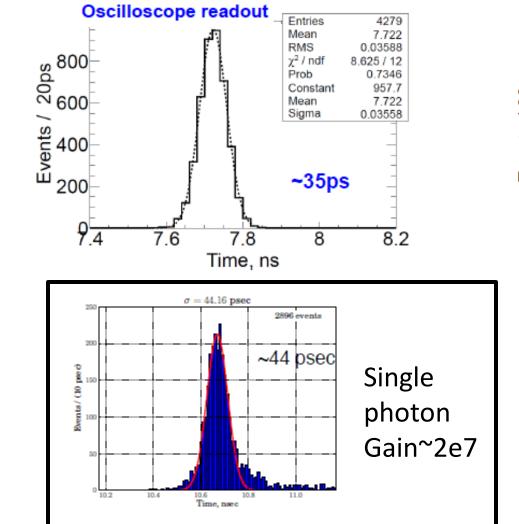

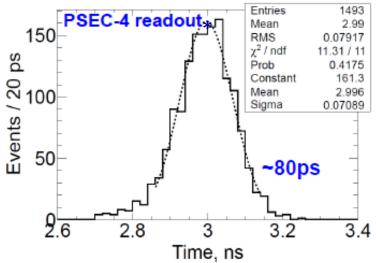

## Time-of-flight resolution

#### 90-cm long anode!

\*using first generation readout board. Newer boards fix some stability issues = better timing

# Lastly: PSEC4 $\rightarrow$ PSEC5

• PSEC5 design (10 Gsa/s & 3.3 microsecond buffer depth) in initial design and simulation stages

| Parameter                         | PSEC4               | PSEC5                        |                       |

|-----------------------------------|---------------------|------------------------------|-----------------------|

| Channels                          | 6                   | 4                            |                       |

| Sampling Rate                     | 4-15  GSa/s         | 5-15  GSa/s                  |                       |

| Primary Samples/channel           | 256                 | 256                          |                       |

| Total Samples/channel             | 256                 | 32768                        | Add 128x buffer depth |

| Recording Buffer Time at 10 GSa/s | 25.6 ns             | $3.3 \ \mu s$                |                       |

| Analog Bandwidth                  | 1.5  GHz            | 1.5 - 2 GHz                  |                       |

| RMS Voltage Noise                 | $700 \ \mu V$       | $< 1 \mathrm{mV}$            |                       |

| DC RMS Dynamic Range              | 10.5 bits           | 10 - 11 bits                 |                       |

| Signal Voltage Range              | 1 V                 | 1 V                          |                       |

| ADC on-chip                       | yes                 | yes                          |                       |

| ADC Clock Speed                   | $1.4  \mathrm{GHz}$ | 1.5 - 2 GHz                  |                       |

| Readout Protocol                  | 12-bit parallel     | serial LVDS: one per channel |                       |

| Readout Clock Rate                | 40 MHz              | 500 MHz                      |                       |

| Average Power Consumption         | 100  mW             | 300-500 mW                   |                       |

| Core Voltage                      | 1.2 V               | 1.2 V                        |                       |